US20050104027A1 - Three-dimensional integrated circuit with integrated heat sinks - Google Patents

Three-dimensional integrated circuit with integrated heat sinks Download PDFInfo

- Publication number

- US20050104027A1 US20050104027A1 US10/965,065 US96506504A US2005104027A1 US 20050104027 A1 US20050104027 A1 US 20050104027A1 US 96506504 A US96506504 A US 96506504A US 2005104027 A1 US2005104027 A1 US 2005104027A1

- Authority

- US

- United States

- Prior art keywords

- integrated circuit

- circuit according

- substrate

- dimensional integrated

- dimensional

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Abandoned

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0652—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05568—Disposition the whole external layer protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13023—Disposition the whole bump connector protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/1605—Shape

- H01L2224/16057—Shape in side view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16104—Disposition relative to the bonding area, e.g. bond pad

- H01L2224/16105—Disposition relative to the bonding area, e.g. bond pad the bump connector connecting bonding areas being not aligned with respect to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16108—Disposition the bump connector not being orthogonal to the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16238—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bonding area protruding from the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

- H01L2224/81815—Reflow soldering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06517—Bump or bump-like direct electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06541—Conductive via connections through the device, e.g. vertical interconnects, through silicon via [TSV]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06551—Conductive connections on the side of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06589—Thermal management, e.g. cooling

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

Definitions

- the present invention relates to a three-dimensional integrated circuit incorporating an integrated heat sink for dissipating heat produced by the integrated semiconductor devices mounted thereon.

- each component should be kept at or below a preset tolerable operating temperature

- memory devices running at a high transfer rate produce heat during operation and the integrated circuit rapidly heats up. Without proper heat dissipation, the IC may overheat and malfunction.

- a heat sink is used for dissipating heat produced by components in an integrated circuit.

- the heat sink has to be in good thermal contact with each component and exposed to the surrounds to maximize heat dissipation.

- a three-dimensional circuit it is difficult to provide sufficient exposure of the heat sink to the surrounds.

- the disclosed invention represents a three-dimensional integrated circuit comprising a heat sink and a set of discrete integrated circuits arranged one above another and system of integrated heat sinks for conducting heat from the integrated circuits to the heat sink.

- Each of said discrete integrated circuits has a heat-conducting substrate and functional elements formed on front and/or rear substrate surface, wherein at least one of the functional elements is a heat-generating element.

- the integrated heat sinks are in thermal contact both with at least one of said substrates and with the heat sink.

- the widths, lengths, thicknesses and thermal conductivities of the substrates of discrete integrated circuits, as well as the number, cross sectional areas, lengths, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the three-dimensional integrated circuit does not exceed a preset tolerable operation temperature determined for previously established intensities of said functional heat-generating elements and their known positions in the three-dimensional integrated circuit.

- Another aspect of the present invention is a monolithic three-dimensional integrated circuit comprising a heat sink and a monolithic multilayer structure representing a system of unit integrated circuits stacked one above another.

- This monolithic multilayer structure is mounted on said heat sink.

- Each of said unit integrated circuits comprises a heat-conducting substrate having front surface and rear surface facing the heat sink.

- Each of these unit integrated circuits comprises a conducting wiring pattern formed on the front substrate surface, and functional elements mounted on front substrate surface and connected to the wiring pattern. One or more of these elements is a heat-generating element.

- Each unit integrated circuit is provided with a protective insulating layer, formed above said wiring pattern and said functional elements, and a planarization layer possessing a flat surface.

- This flat surface of the planarization layer which is most distant from the front surface of the substrate, serves a base for the subsequent unit integrated circuit of said stacked system.

- Said three-dimensional monolithic integrated circuit also contains a system of integrated heat sinks. Each integrated heat sink is in thermal contact with said heat sink and penetrates into the monolithic multilayer structure, thus providing thermal contact with at least one substrate of said unit integrated circuits.

- the substrate thicknesses and thermal conductivities, as well as the number, cross sectional areas, lengths, arrangement, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the three-dimensional monolithic integrated circuit would not exceed a preset tolerable operation temperature determined for preliminarily established intensities of the said functional heat-generating elements and their known positions in the three-dimensional monolithic integrated circuit.

- FIG. 1 a is a schematic diagram of a three-dimensional integrated circuit representing a system of several discrete integrated circuits.

- FIG. 1 b is a sectional view of the integrated circuit of FIG. 1 a taken along the line A-A.

- FIG. 2 shows the main types of electrically conducting elements for connecting to neighboring discrete integrated circuits in a three-dimensional integrated circuit.

- FIG. 3 shows an example of electrical connections between discrete integrated circuits in a three-dimensional integrated circuit via electrically conducting elements of various types.

- FIG. 4 shows an axonometric image of a system of substrates, integrated heat sinks, and a heat sink according to the present invention.

- FIGS. 5 a - 5 d are cross-sections of arched solder joint with pads according to the present invention, during intermediate fabrication steps.

- FIG. 6 is a schematic diagram of a three-dimensional integrated circuit with integrated heat sinks according to the present invention, in which thermal contacts are obtained with the use of arched solder joints.

- FIGS. 7 a - 7 b show schematic diagrams of the arched solder joints with dimensions according to the present invention.

- FIG. 8 is a schematic diagram of a three-dimensional monolithic integrated circuit according to the present invention.

- FIG. 9 shows the typical temperature dependence of resistance of an semiconductor thin crystal film sample.

- FIG. 10 shows a thin-film transistor structure with top source and drain contacts.

- FIG. 11 shows a thin-film transistor structure with bottom source and drain contacts.

- One preferred embodiment of the disclosed invention is a three-dimensional integrated circuit (IC) comprising a heat sink, a set of discrete ICs arranged one above another, and system of integrated heat sinks for conducting heat from the integrated circuits to the heat sink.

- This set of discrete ICs is mounted on said heat sink.

- Each of said discrete ICs has a heat-conducting substrate, and functional elements formed on front and/or rear substrate surface, wherein at least one of the functional elements is a heat-generating element.

- the three-dimensional IC also comprises a system of integrated heat sinks in thermal contact with at least one of said substrates and with the heat sink.

- the widths, lengths, thicknesses and thermal conductivities of the substrates of discrete integrated circuits, as well as the number, cross sectional areas, lengths, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the said three-dimensional IC will not exceed a preset tolerable operation temperature determined for preliminarily established intensities of the said heat-generating elements and their known positions in the three-dimensional IC.

- the thermal fluxes from heat sources first spread over heat-conducting substrates, then enter into integrated heat sinks, and are eventually dissipated in the heat sink.

- the functional elements of discrete IC are thin-film passive elements (capacitors, resistors, and inductive coils) and active semiconductor devices (transistors and diodes).

- At least one substrate is made of Al 2 O 3 based ceramics.

- the substrate of the bottom discrete integrated circuit is in direct thermal contact with the heat sink.

- the present invention provides a three-dimensional IC in which at least one said functional element is made using a semiconductor thin crystal film (SCTCF) formed by rodlike supramolecules composed of at least one organic compound with conjugated ⁇ -system, wherein a crystal structure of the film has an intermolecular spacing of 3.4 ⁇ 0.3 ⁇ in the direction of at least one crystal axis.

- SCTCF semiconductor thin crystal film

- a necessary condition is the presence of a developed system of conjugated ⁇ -electronic bonds between conjugated aromatic rings of the molecules and the presence of groups (such as amine, phenol, ketone, etc.) lying in the plane of the molecule and involved into the aromatic system of bonds.

- the molecules and/or their molecular fragments possess a planar structure and are capable of forming supramolecules in solutions.

- Another necessary condition is the maximum overlap of ⁇ -orbitals in the stacks of supramolecules.

- FIGS. 1 a and 1 b illustrate one possible embodiment of a three-dimensional (3D) integrated circuit according to the disclosed invention.

- the three-dimensional IC comprises a set of discrete integrated circuits, each formed on a separate substrate ( 1 - 4 ) made of heat-conducting material. Al 2 O 3 based ceramics offers an example of such a material. In the description to follow, these discrete integrated circuits are referred to as elementary ICs. Three-dimensional integrated circuits are not restricted to four discrete integrated circuits as depicted in FIG. 1 a .

- Each discrete substrate accommodates an IC topology which includes heat-generating elements ( 1 a - 1 d on substrate 1 , 2 a - 2 d on substrate 2 , etc.).

- the discrete integrated circuits can be electrically connected to each other (neither wiring topologies not interconnections are depicted in FIG. 1 ).

- the substrates are fastened with heat-conducting glue or solder layers 5 to integrated heat sinks 6 which in turn are connected to a common heat sink 7 so as to form a 3D structure.

- Coating 8 protects the three-dimensional IC structure.

- Active elements in such ICs can be discrete diodes and transistors, as well as microassemblies (each including several diodes and/or transistors) made of inorganic or organic materials.

- FIG. 1 a the functional heat-generating elements of ICs are depicted schematically, with black areas representing regions containing heat sources.

- the main heat source is the region of a conducting channel between source and drain. In this region, the heat is generated as a result of current passage in the course of transistor operation.

- Another heat source in a TFT is related to the gate circuit. Heat generated in the functional heat-generating elements is initially dissipated in the corresponding substrates. Arrows in FIGS. 1 a and 1 b indicate the directions of thermal fluxes in the 3D structure under consideration.

- Heat liberated in the bottom discrete IC is transferred directly to the heat sink, while heat generated in the other discrete ICs ( 1 , 2 , 3 and other analogous discrete discrete circuits) is first transferred to integrated sinks 6 and then to the common heat sink 7 .

- FIG. 1 b shows a cross section of the 3D integrated circuit of FIG. 1 a taken along the line AA′.

- the integrated heat sinks integrated into the three-dimensional integrated IC have a rectangular cross section.

- the cross section of these integrated heat sinks can be of arbitrary shape selected from circle, ellipse, square, rectangle, or polygon.

- the geometry of elements of a 3D integrated circuit according to this invention can vary. Variable parameters include the thicknesses of the regions of functional heat-generating elements representing heat sources, the thicknesses of the substrates under discrete ICs, and the dimensions (height, width, thickness) of the integrated heat sinks. By appropriately selecting these parameters, it is possible to provide for the optimum thermal regime of operation of the disclosed 3D integrated circuit, to assure that the working temperature of any active element in the 3D scheme will not exceed a preset maximum tolerable operation temperature.

- FIG. 2 shows the main types of electrically conducting elements that can be used for connecting neighboring discrete integrated circuits so as to provide for 3D integration.

- FIG. 2 shows a single discrete IC comprising a substrate 1 with topological wiring patterns formed on the rear and front surfaces.

- Metallization layers 9 and 10 represent these patterns.

- both rear and front substrate surfaces bear protective dielectric layers 11 and 12 respectively.

- the rear protective layer 11 also includes contact pads 13

- the frontal protective layer 12 includes analogous contact pads 14 . These contact pads are used to provide for the electric connections between neighboring discrete integrated circuits.

- metallized (metal-filled) window 15 provides for the connection between topological wiring pattern of the front surface and one of the contact pads 14 .

- metallized window 16 connects topological wiring pattern of the rear surface to one of the front contact pads 14

- metallized window 17 connects one of the frontal contact pads 14 to one of the rear pads 13

- metallized window 18 connects topological wiring pattern of the front surface to one of the rear contact pads 13

- metallized window 19 connects topological wiring pattern of the rear surface to one of the rear contact pads 13 .

- Said discrete IC is fastened to integrated heat sinks 6 with a layer of heat-conducting glue or solder 5 , which provides for a good thermal contact with low thermal resistance.

- the integrated heat sinks 6 are in good thermal contact with the heat sink 7 .

- Arrows in FIG. 2 indicate the paths of thermal fluxes in the given 3D integrated circuit.

- FIG. 3 shows how various types of electrically conducting elements via metallized windows can be used for connecting several discrete integrated circuits in a 3D structure.

- FIG. 3 shows the electrically conducting elements between three discrete ICs ( 1 - 3 ).

- the wiring patterns of the discrete ICs should contain connection points that have to be linked during assembly of the 3D integrated circuit.

- a system of metallized windows and contact pads 20 connects a topological pattern of the front surface of IC 1 to that of the front surface of IC 2

- the system of metallized windows and contact pads type 21 connects a topological pattern of the rear surface of IC 1 to that of the front surface of IC 2

- the system 22 connects a topological pattern of the front surface of IC 1 to that of the rear surface of IC 2 .

- system 23 connects a topological pattern of the rear surface of IC 1 to that of the front surface of IC 3

- system 24 connects the front surface of IC 2 to front surface of IC 3

- system 25 connects the rear surface of IC 2 to the rear surface of IC 3 .

- FIG. 4 shows a 3D integrated circuit according to the present invention, comprising first 1 and second 2 substrates, integrated heat sinks 6 , and a heat sink 7 .

- Substrates 1 and 2 contain rows of pads 26 and integrated heat sinks 6 contain rows of pads 27 connected to elongated pad extensions 28 .

- the pads may differ in the number, dimensions, and arrangement on substrates 1 and 2 . Although square pads are depicted in FIG. 4 , they can be of any shape.

- the rows of pads can be also be present on the rear surfaces of substrates 1 and 2 , as well as on their edges (this variant is not shown). Said pairs of pads can be used for making thermal contacts of different substrates with integrated heat sinks.

- Both substrate 1 and substrate 2 may represent integrated circuit chips, printed circuit boards, multi-layer ceramic substrates, or any other substrates used in microelectronics. Methods for the formation of pads on such substrates are well known and need not be described further herein.

- the spacing of pads 27 in the rows on integrated heat sinks 6 preferably corresponds to the spacing of the corresponding row of pads 26 in substrates 1 or 2 . It should be noted that the pad pitches need not be identical, since one substrate can be mounted on heat sink at an angle, so that one pad pitch may be less than the other pitch.

- pads in at least one of the first and second rows are provided with elongated pad extensions, which are narrower than the pads.

- the row of pads 27 has such a system of elongated pad extensions 28 , which are narrower than the pads.

- Each elongated pad extensions 28 is connected to the corresponding pad 27 in the row.

- the pad extensions, as well as the pads, are preferably covered with a layer of solder.

- FIGS. 5 a - 5 d show the cross sections of arched solder joint with pads according to the present invention, involving substrate 1 and integrated heat sink 6 , during intermediate fabrication steps.

- substrate 1 is nonparallel to integrated heat sink 6 and the edge of this substrate is close to integrated heat sink 6 .

- the substrate contains a row of pads 26

- integrated heat sink 6 contains a row of pads 27 adjacent to and arranged along the edge of substrate 1 . It will also be understood that two, three, or more substrates containing the appropriate rows of pads can be mutually oriented for assembly.

- pads in one of the rows have elongated extensions 28 .

- Such pad extensions can be formed on substrate 1 and/or integrated heat sink 6 or both, depending on the particular geometry of the pads, the volumes of solder bumps that have to be formed, and other arched solder joint parameters.

- pads 27 and the associated elongated pad extensions 28 are coated with a layer of solder 29 .

- FIG. 5 a depicts integrated heat sink 6 oriented perpendicularly to substrate 1 .

- the integrated heat sink and substrate can be oriented at an angle relative to one another.

- FIG. 5 a shows a bonding layer 5 , which can be used to attach the integrated heat sink and substrate to one another prior to soldering.

- the bonding layer may be glue or flux or any other common adhesive used in the microelectronic industry.

- the material of bonding layer 5 can possess high thermal conductivity, thus favoring the formation of a thermal contact with lower thermal resistance between the substrate and the integrated heat sink.

- a clamp or other fixture can be used to hold the substrate and heat sink together in the absence of a bonding layer, or the force of gravity may hold them in contact.

- solder layer 29 on pads 27 and pad extensions 28 can be formed by various methods. Techniques for forming a solder layer on pads and extended regions could be found for example in WO 9,631,905 “A Solder Bump Structure for Microelectronic Substrate” and U.S. Pat. No. 6,389,691 “Methods for Forming Integrated Redistribution Routing Conductors and Solder Bumps”.

- FIGS. 5 b , 5 c and 5 d illustrate the reflow soldering process.

- a solder bump 30 forms on pad 27 as solder 29 flows from over elongated pad extension 28 to pad 27 in the direction shown by arrow 33 .

- Solder flows from the elongated pad extension onto the pad due to the surface tension within the solder, which causes the flowing solder to flow from a relatively thin extension to the relatively wide pad, as described in WO 9,631,905 and U.S. Pat. No. 6,389,691.

- a solder bump 31 of increasing volume forms since more solder is supplied from elongated pad extension 28 to pad 27 .

- the arched solder joint 32 may be considered as a part of a ring (here, a quarter-ring arc).

- the arched solder joint preferably possesses a uniform transverse cross section, which represent an excellent conductor for thermal flux. In other configurations, the cross-section need not be uniform. For example, both pads may be rectangles rotated 90° relative to one another, so that the arched solder joint is also rotated by 90°.

- the arched solder joints can be used for mechanical connections in the microelectronic packages.

- solder layer 29 is formed using a patterned plating template that defines regions of differing internal pressures in the molten solder. During reflow, the molten solder flows preferentially to the low-pressure regions, thereby forming a large bump that extends beyond the edge of the substrate. The bump can wet the solder pad and form an arched solder joint that provides thermal connection and/or mechanically supports the package.

- the method illustrated in FIGS. 5 a - 5 d begins with the formation of a solder bump on integrated heat sink 6 .

- solder bump can be as well formed on substrate 1 and then expanded to contact a pad on integrated heat sink 6 .

- solder bumps may be formed on both integrated heat sink and substrate, and then expand to contact one another and thereby form the arched solder joint 32 .

- Arched solder joints 32 offer several thermal and mechanical advantages. The arched solder joint may also provide structural support, while allowing some compliance for improved reliability, in contrast to the conventional fillet type joints.

- the disclosed package may provide many new system assembly options with low weight, compactness, and good thermal management, together with low cost and potentially enhanced performance.

- One application of the technology is a compact, low cost multi-chip module assembly where there may be significant reduction in the area devoted to the second level package.

- a typical application may be for large-scale memories.

- Another application may be in mixed signal assembly integration.

- an assembly may be provided with mixed analog/digital/microwave systems in a compact package, as illustrated below.

- FIG. 6 is a schematic diagram illustrating a preferred embodiment of the three-dimensional IC with integrated heat sinks according to the present invention, in which thermal contacts are obtained with the use of a solder material.

- the thermal contacts of substrates 1 and 2 with integrated heat sink 6 and the thermal contact of this integrated heat sink 6 and the heat sink 7 are provided by arched solder joints 60 .

- the bonding layer 59 between the edge of the integrated heat sink 6 and the heat sink 7 provides for an additional thermal contact.

- the adhesive material of layer 59 must possess high thermal conductivity.

- other elements of the 3D integration in FIG. 6 are not depicted.

- thermal flux management is important for this technology.

- Each of these solder joints can be modeled by a series of thermal resistances involving the solder joint and the pad resistance on each end.

- a thermal model for this 3D technology with round pads is shown in FIG. 7 a .

- This model assumes the contact pads to be round, of radius r pad and thickness l pad , and possess a thermal conductivity of k pad , while the solder material possesses a thermal conductivity of k solder .

- R total 4 ⁇ l pad /( ⁇ L ⁇ k pad ⁇ r pad )+2 ⁇ /( ⁇ L ⁇ k solder ).

- the first term represents the thermal resistance of two contact pads and the second, that of the solder.

- FIG. 7 b illustrates a thermal model for the 3D package with square pads is shown in FIG. 7 b .

- This model assumes the contact pads to be squares with a side length of w pad , a thickness of l pad , and a thermal conductivity of k pad , while the solder material possesses a thermal conductivity of k solder .

- R total 2 ⁇ l pad /( L ⁇ k pad ⁇ w pad )+ ⁇ /(2 ⁇ L ⁇ k solder ).

- the first term represents the thermal resistance of two contact pads and the second, that of the solder.

- An analysis of this relation shows that the thermal resistance of the solder is independent of the cross section radius, i.e. of the square side length (w pad ).

- the thermal resistance of the contact pads increases with decreasing w pad . Therefore, it is possible that, for sufficiently small w pad , the thermal resistance of the contact pads will exceed that of the solder bumps. In order to avoid this, w pad has to be limited by the condition that the thermal resistance of the contact pads must not exceed that of the solder bumps.

- FIG. 8 presents a schematic diagram of another possible embodiment of the 3D integrated circuit according to the present invention.

- Each layer in this structure is formed immediately on the preceding layer, so that the 3D structure is monolithic.

- This monolithic 3D integrated circuit is carried on plate 34 representing a heat sink.

- the heat sink should be made of a material possessing high thermal conductivity, such as copper, which can simultaneously serve as the electric “ground” of the IC.

- the base carries a layer of dielectric 35 , which also possesses high thermal conductivity (a candidate material is Al 2 O 3 ceramics).

- the dielectric layer contains windows (holes), which can be either metallized (to provide for electrical ground 36 ) or made of a material which possesses high thermal conductivity (acting as integrated heat sinks 37 ).

- Integrated heat sinks can be made either of Al 2 O 3 based ceramics or of any other good heat conductor. Although not shown, the heat sink may be cooled by circulating a fluid therethrough.

- a 3D monolithic structure of the type under consideration may contain several dielectric layers.

- the IC depicted in FIG. 8 contains two such layers ( 35 and 54 ) bearing all the active (diodes, transistors) and passive (capacitors, inductances, and resistors) elements of the 3D circuit.

- FIG. 8 shows an IC including a thin-film transistor and a contact area 44 formed on the dielectric layer 35 and grounded via metallized window 36 .

- the transistor contains source 38 and drain 39 electrodes formed immediately on the dielectric layer 35 (the source is grounded via metallized window 36 ).

- the transistor may contain a layer of inorganic or organic semiconductor 40 , insulating layer 41 , gate electrode 42 , and a protective layer 43 .

- the 3D monolithic integrated circuit of FIG. 8 contains a planarization layer 45 carrying the second dielectric layer 54 .

- This layer bears the second thin-film transistor with source 46 and drain 47 electrodes, a layer of organic semiconductor 48 , an insulating layer 49 , and gate electrode 50 .

- the drain of the first thin-film transistor is connected to the source of the second transistor via metallized window 51 formed in the protective layer 43 , planarization layer 45 , and dielectric layer 54 .

- the IC contains protective layers for the transistor 52 and the whole structure 53 .

- the dimensions of all elements of the monolithic 3D integrated-circuit can be considered as variable parameters.

- the 3D integrated circuits depicted in FIGS. 1 and 8 are not the only possible embodiments of the disclosed invention.

- active thin-film elements based on inorganic semiconductors can be incorporated into the integrated circuit together with organic thin-film transistors and diodes.

- the 3D structure will contain additional layers of inorganic semiconductors (e.g., silicon).

- the number of integrated heat sinks is not limited by four as in FIG. 1 b or two as in FIG. 8 . The arrangement and number of such integrated heat sinks is selected so as to provide for the normal thermal regime of operation for all elements of the integrated circuit.

- At least one functional heat-generating element is a semiconductor transistor.

- At least one functional heat-generating element is a semiconductor diode comprising a semiconductor layer and electrode (cathode and anode) layers. These layers can also be made of both organic and inorganic materials. Therefore, there are three possible variants, whereby (i) all layers in the transistor structure are made of organic materials, (ii) all layers are made of inorganic materials, or (iii) some layers are organic and the others are inorganic.

- At least one functional heat-generating element is a thin film resistor.

- At least one integrated heat sink is made of an Al 2 O 3 based ceramic material.

- At least one integrated heat sink has a front surface facing said discrete integrated circuits and an edge face facing the heat sink.

- Said integrated heat sink has the shape of the cross section parallel to rear surface of said substrates, which shape is selected from the list comprising circle, ellipse, square, rectangle, polygon, or any combination thereof.

- the disclosed three-dimensional IC further comprises at least one bonding layer made of a heat-conducting adhesive material. This layer is located between the front surface at least of one of said integrated heat sinks and the edge face at least of one of said substrates. Said substrate is oriented relative to integrated heat sink so that the edge face of this substrate is adjacent said integrated heat sink.

- the three-dimensional integrated circuit further comprises at least one bonding layer made of a heat-conducting adhesive material. Said bonding layer is located between said heat sink and the edge face at least of one of said integrated heat sinks.

- the integrated heat sink is oriented so that its edge face is adjacent to said heat sink.

- the three-dimensional integrated circuit further comprises at least one set of arched solder joints forming thermal contacts between the front surface of at least one of said integrated heat sinks and at least one surface of at least one of said substrates.

- said arched solder joints have nonuniform cross sections along their lengths.

- the three-dimensional integrated circuit further comprises at least two rows of pads, wherein the first row of pads is positioned on said integrated heat sink and the second row of pads on said substrate adjacent to the first row of pads and arranged along the edge face of said substrate, said pads in at least one of these rows having elongated pad extensions which are narrower than the pads and said set of arched solder joints connects said pads of first row with pads of second row.

- the three-dimensional integrated circuit further comprises at least one bonding layer made of a heat-conducting adhesive material and located between said heat sink and the edge face at least of one of said integrated heat sinks.

- the disclosed invention makes use of several main types of conducting elements between discrete ICs, which allow these ICs to be electrically connected into a three-dimensional IC. Some possible variants are considered below.

- At least one discrete integrated circuit comprises the conducting wiring pattern and the functional elements formed on the front and rear substrate surfaces.

- Said discrete integrated circuit further comprises a front protective dielectric layer covering the wiring pattern and the functional elements situated on the front surface of the substrate, and a rear protective dielectric layer covering the wiring pattern and the functional elements situated on the rear surface of the substrate.

- at least one discrete IC comprises at least one frontal contact pad situated on said front protective dielectric layer. This discrete IC also contains at least one electrically conducting element penetrating through said front protective dielectric layer and the substrate so as to connect the wiring pattern (topology) of the rear surface of said substrate to said front contact pad.

- At least one discrete IC contains at least one rear contact pad, situated on said rear protective dielectric layer, and at least one electrically conducting element penetrating through said rear protective dielectric layer and through the substrate of this IC. This conductor connects the wiring pattern of the front surface of said substrate to said rear contact pad.

- At least one discrete IC further comprises at least one front contact pad situated on said front protective dielectric layer at least one rear contact pad situated on said rear protective dielectric layer.

- This discrete IC also contains at least one electrically conducting element penetrating through the front protective dielectric layer, the substrate, and the rear protective dielectric layer so as to connect said frontal contact pad to said rear contact pad.

- At least one discrete IC further comprises at least one frontal contact pad, situated on said frontal protective dielectric layer, and at least one rear contact pad situated on said rear protective dielectric layer.

- This discrete IC also contains at least one electrically conducting element penetrating through the frontal protective dielectric layer, the substrate, and the rear protective dielectric layer of this IC. This conductor connects said frontal contact pad to at said rear contact pad.

- At least one discrete IC comprises the conducting wiring pattern and the functional elements formed at least on the front substrate surface.

- Said discrete IC further comprises a front protective dielectric layer covering said wiring pattern and functional elements connected to the said wiring pattern, and at least one front contact pad, situated on said front protective dielectric layer.

- This discrete IC also contains at least one electrically conducting element penetrating through said front protective dielectric layer, which connects the wiring pattern to said front contact pad.

- At least one discrete integrated circuit comprises the conducting wiring pattern formed at least on the rear substrate surface.

- This discrete integrated circuit further comprises a rear protective dielectric layer covering said wiring pattern and functional elements connected to the said wiring pattern, and at least one rear contact pad, situated on said rear protective dielectric layer.

- Said discrete IC also contains at least one electrically conducting element penetrating through said rear protective dielectric layer, which connects the wiring pattern to said rear contact pad.

- the three-dimensional integrated circuit further comprises a first protective dielectric layer covering the conducting wiring pattern and functional elements of the first discrete integrated circuit. Furthermore, said three-dimensional integrated circuit further comprises at least one front contact pad, situated on said first protective dielectric layer. Then, said three-dimensional integrated circuit further comprises a second protective dielectric layer covering the conducting wiring pattern and functional elements of the second discrete integrated circuit. Finally, the three-dimensional integrated circuit further comprises at least one rear contact pad, situated on said second protective dielectric layer, and at least one electrically conducting element, which connects said rear contact pad with said front contact pad.

- Another preferred embodiment of the present invention is a monolithic three-dimensional integrated circuit comprising a heat sink and a monolithic multilayer structure representing a system of unit ICs stacked one above another.

- This monolithic multilayer structure is mounted on a heat sink.

- Each of said unit ICs has a heat-conducting substrate having rear surface facing the heat sink and the front surface.

- Each of these unit ICs has a conducting wiring pattern (topology), formed on front substrate surface, and functional elements mounted on front substrate surface and connected to the wiring pattern, at least one of these elements being a functional heat-generating element representing a heat source.

- each unit IC is provided with a protective insulating layer formed above said wiring pattern and said functional elements, and a planarization layer formed above the protective layer.

- the flat surface of the planarization layer serves a base for the subsequent unit IC of said stacked system.

- Said three-dimensional monolithic IC also comprises a system of integrated heat sinks, wherein each integrated heat sink is in thermal contact with said heat sink and penetrate into the monolithic multilayer structure, thus providing thermal contact with at least one substrates of said unit ICs.

- the substrate thicknesses and thermal conductivities, as well as the number, cross sectional areas, lengths, arrangement, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the three-dimensional monolithic IC would not exceed a preset tolerable operation temperature determined for preliminarily established intensities of the said heat-generating elements and their known positions in the three-dimensional monolithic IC.

- thermal fluxes from the heat sources first spread over heat-conducting substrates, then enter into integrated heat sinks, and are eventually dissipated in the heat sink.

- the arrangement of integrated heat sinks in the monolithic structure should provide heat removal from functional heat-generating elements.

- the arrangement of integrated heat sinks depends on a position and thermal power of functional heat-generating elements in the three-dimensional monolithic IC. Said arrangement is characterized by number of integrated heat sinks, which environ each of said functional heat-generating elements, and by average distance between said integrated heat sinks and said functional heat-generating element. For this purpose the integrated heat sinks are positioned adjacent to the functional heat-generating elements. The more thermal power of functional heat-generating element, the more said number and less said distance.

- said number of integrated heat sinks, located around of everyone functional heat-generating element, and average distance between said integrated heat sinks and said functional heat-generating element are selected so as to ensure that the temperature in any region of the three-dimensional monolithic integrated circuit would not exceed a preset tolerable operation temperature.

- This is achieved through the formation of integrated heat sinks by the known technological means immediately on the heat sink, which provides for a low thermal resistance of the thermal contacts between the integrated heat sinks and the heat sink.

- the integrated heat sinks are created stage by stage in the course of formation of adjacent IC units of said multilayer structure. According to this, known technological methods are used to open windows after the formation of a sequential layer and to fill these windows with a selected heat-conducting material which forms a part of the integrated heat sink.

- the next layer of said multilayer structure is formed and the windows, matched to those in the preceding layer, are opened and filled with the heat-conducting material to obtain the corresponding part of the integrated heat sink.

- This cycle is repeated in each stage of assembly of the multilayer structure.

- a system of integrated heat sinks penetrating into the said monolithic three-dimensional IC structure is formed.

- the disclosed method of forming integrated heat sinks allows thermal contacts with low thermal resistances to be obtained.

- At least one functional heat-generating element represents a semiconductor thin-film transistor.

- Said transistor includes a semiconductor layer, an insulating layer, and electrode layers (source, drain, and gate). These layers can be made of both organic and inorganic materials.

- at least one functional heat-generating element represents a semiconductor diode comprising a semiconductor layer and electrode (cathode and anode) layers.

- at least one functional heat-generating element represents a thin-film resistor.

- At least one integrated heat sink is made of Al 2 O 3 based ceramics.

- At least one integrated heat sink has the shape of the cross section parallel to the front surface of said substrate selected from the list comprising circle, ellipse, square, rectangle, polygon, or any combination thereof.

- at least one substrate of at least one unit integrated circuit further comprises at least one conducting element. Said conducting element is formed penetrating said substrate and contacting with wiring pattern (topology) arranged on the front surface of said substrate.

- the disclosed monolithic three-dimensional IC contains at least one electrically conducting element situated between two adjacent substrates.

- At least one planarization layer is made of a thermoelastic material. Such materials are capable of passing to a liquid (flowable) state in a certain temperature interval. In this state, the surface of said thermoelastic material becomes flat.

- the present invention provides the three-dimensional integrated circuit having the discrete integrated circuits or the monolithic three-dimensional IC, which contain at least one functional element such as TFT made using a semiconductor thin crystal film (SCTCF).

- SCTCFs are formed by rodlike supramolecules composed of at least one organic compound with conjugated ⁇ -system, wherein a crystal structure of the film has an intermolecular spacing of 3.4 ⁇ 0.3 ⁇ in the direction of at least one crystal axis.

- This semiconductor thin crystal film (SCTCF) is based on an aromatic polycyclic compound and has the electron-hole type of conductivity.

- a condition is the presence of a developed system of ⁇ -conjugated bonds between conjugated aromatic rings of the molecules and the presence of groups (such as amine, phenol, ketone, etc.) lying in the plane of the molecule and involved into the aromatic system of bonds.

- the molecules and/or their molecular fragments possess a planar structure and are capable of forming supramolecules in solutions.

- Another condition is the maximum overlap of ⁇ -orbitals in the stacks of supramolecules.

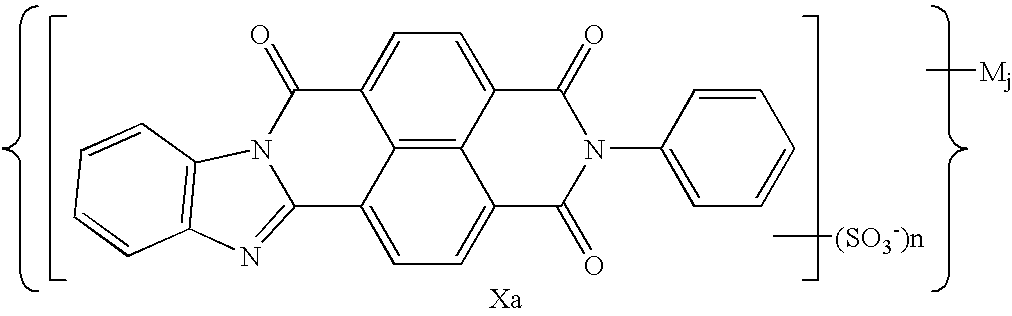

- Aromatic compounds suitable for the obtaining of SCTCFs are characterized by the general formula ⁇ R ⁇ ⁇ F ⁇ n , where R is a polycyclic core featuring a ⁇ -electron system, F is a modifying functional group ensuring solubility of a given compound in nonpolar or polar solvents (including aqueous media), and n is the number of functional groups.

- these organic compounds include the following:

- n is an integer in the range of 1 to 4 and p is an integer in the range of 0 to 6;

- Y is individually selected from the group consisting of H, Cl, F, Br, Alk, OH, OAlk, NO 2 and NH 2 ;

- M is a counterion; and

- j is the number of counterions in the molecule; for n>1, different counterions M can be involved;

- X 1 , X 3 , X 4 , X 5 , X 6 , X 7 , X 8 are substituents from the group including H, OH, SO 3 H, such that at least one of these substituents is different from H;

- Y is a substituent from the series H, Cl, F, Br, Alk, OH, OAlk, NO 2 , NH 2 and p is an integer in the range of 0, 1, 2, 3 and 4;

- n is one of the group including 0, 1, 2, such that at least one of fragments A 1 or A 2 comprises at least one sulfogroup;

- M is counterion; and j is the number of counterions in the molecule; for n>1, different counterions M can be involved;

- X 1 , X 3 , X 4 , X 5 , X 6 , X 7 , X 8 are substituents from the group including H, OH, SO 3 H;

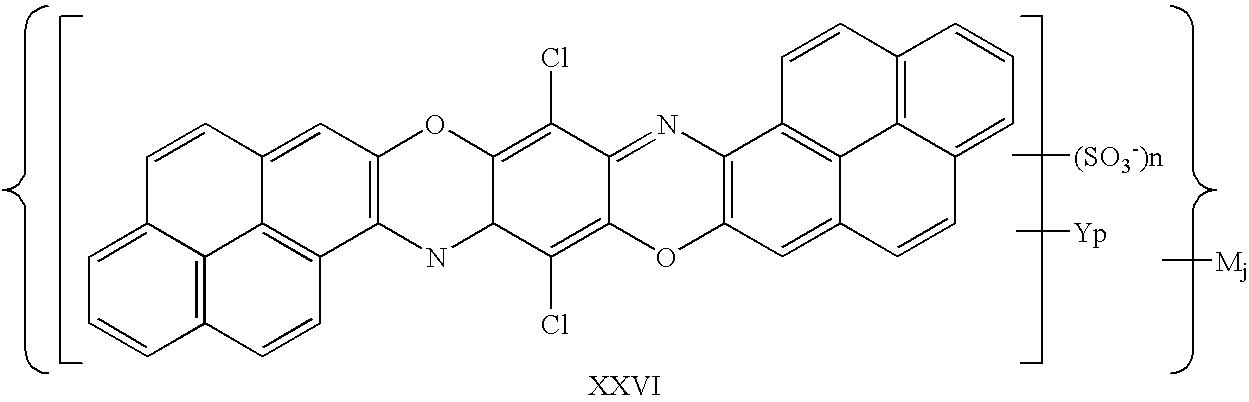

- Z is a bridge closing new heterocyclic systems chosen from the series —O—, —SO 2 —, —SO 2 —O—;

- Y is a substituent from the series H, Cl, F, Br, Alk, OH, OAlk, NO 2 , NH 2 and p is an integer in the range of 0, 1, 2, 3 and 4;

- n is one of the group including 0, 1, 2, such that at least one of fragments A 1 or A 2 comprises at least one sulfogroup;

- M is counterion; and j is the number of counterions in the molecule; for n>1, different counterions M can be involved;

- n is an integer in the range of 1 to 4 and p is an integer in the range of 0 to 8; Y is individually selected from the group consisting of H, Cl, F, Br, Alk, OH, OAlk, NO 2 and NH 2 ; M is a counterion; and j is the number of counterions in the molecule; for n>1, different counterions M can be involved;

- sulfoderivatives of fused polycyclic heteroaromatic compounds comprising five or six members with N or O or both (pyrrole, pyridine, oxazole, furan, oxazine, azine, chromone, pyridopyrimidine) with the structural formulas XXV-XXVIII:

- n is an integer in the range of 1 to 4 and p is an integer in the range of 0 to 8; Y is individually selected from the group consisting of H, Cl, F, Br, Alk, OH, OAlk, NO 2 and NH 2 ; M is a counterion; and j is the number of counterions in the molecule; for n>1, different counterions M can be involved.

- a low sensitivity of the disclosed monolithic three-dimensional IC with respect to temperature variations is achieved, in particular, due to the fact that said SCTCFs possess higher temperature stability as compared to the conventional materials. Indeed, SCTCFs can be treated at temperatures of up to 700° C. without any significant change in the electrical properties.

- the ability of the disclosed three-dimensional ICs to retain their working properties at high ambient temperatures allow these ICs to be used in electronic devices intended for steel making industry (melt level sensors), in aerospace technologies (electronic transducers for engine nozzles), and in many other high-temperature applications.

- SCTCFs implemented in the disclosed monolithic three-dimensional ICs consists in the possibility of using printing technology for the creation of functional semiconductor elements of the discrete ICs.

- Said SCTCFs can be obtained by a method, called Cascade Crystallization Process developed by Optiva Technology. The process is further described in detail in P. Lazarev and M. Paukshto, Proceedings of the 7 th International Workshop “Displays, Materials and Components ” (Kobe, Japan, Nov. 29-Dec. 1, 2000), pp. 1159-1160.

- this method such an organic compound dissolved in an appropriate solvent forms a colloidal system which is lyotropic liquid crystal solution, in which molecules are aggregated into supramolecules constituting kinetic units of the system.

- This liquid crystal phase is essentially a precursor of the ordered state of the system, from which a solid anisotropic crystal film is formed in the course of subsequent alignment of the supramolecules and removal of the solvent.

- the film is also named thin crystal film or TCF.

- a method stipulated for the synthesis of anisotropic semiconducting thin crystal films from a colloidal system with supramolecules includes the following stages:

- this stage can also include an additional thermal treatment (annealing) characterized by the duration, character, and temperature, which are selected so as to ensure full or at least partial removal of water molecules from said crystal hydrate structure, while retaining the structure of supramolecules and crystalline structure of conjugated aromatic crystalline layer intact.

- annealing additional thermal treatment

- the molecular planes are parallel to each other and the molecules form a three-dimensional crystal structure, at least in a part of the layer. Optimization of the production technology may allow the formation of a single-crystal film.

- the SCTCF thickness usually does not exceed 1 ⁇ m.

- the film thickness can be controlled by changing the content of a solid substance in the applied solution and by varying the applied layer thickness. In order to obtain the films possessing desired optical characteristics, it is possible to use mixed colloidal systems (such mixtures can form joint supramolecules).

- the mixing of said organic compounds in solutions results in the formation of mixed aggregates of variable composition.

- the analysis of X-ray diffraction patterns for the mixtures allow us to judge about the molecular packing in supramolecules by the presence of a characteristic diffraction peak corresponding to intermolecular spacing in the range from 3.1 to 3.7 ⁇ . In general, this value is common for aromatic compounds in the form of crystals and aggregates. The peak intensity and sharpness increase in the course of drying, however, no changes in the peak position are observed. This diffraction peak corresponds to the intermolecular spacing within aggregates (stacks) and has been observed in the X-ray diffraction patterns of various materials.

- the mixing is favored by the planar structure of molecules or their fragments and by the coincidence of one molecular dimension in the organic compounds under consideration.

- the organic molecules possess a long-range order in one direction, which is related to the alignment of supramolecules on the substrate surface. As the solvent is evaporated, it is energetically favorable for the molecules to form a three-dimensional crystal structure.

- Thin crystal films obtained by the method described above exhibit electric conductivity of two types: electron, related to the system of ⁇ -conjugated bonds in supramolecules, and ionic, related to the ion component of the crystalline film and the presence of free water (solvent). As the water content in the film decreases in the course of drying, the ion component drops; using additional annealing step, this component can be completely eliminated.

- the electron conductivity component of SCTCFs depends primarily on the length of supramolecules that can be controlled in the course of manufacture. In the presence of an electric field, the free electrons can drift along supramolecules (stacks), while the transitions between stacks are determined by tunneling effects. Thus, SCTCFs possess a pronounced anisotropy of the electrical properties.

- SCTCFs possess a high degree of optical anisotropy as well.

- Such films exhibit the properties of E-type polarizers, which are related to peculiarities of the optical absorption of supramolecular complexes, and behave as retarders (al known as phase-shifting films) in the spectral ranges where the absorption is insignificant.

- the retarding properties of these anisotropic films are related to their birefringence (also known as double refraction) that is, to a difference in refractive indices measured in the direction of application of the LLC solution onto a substrate and in the perpendicular direction.

- Films formed from the LLC systems based on light-fast organic molecules are characterized by high thermal stability and light resistance.

- FIG. 9 shows the temperature dependence of a SCTCF sample obtained as described above and measured in the direction perpendicular to the direction of application.

- the resistance decreases with increasing temperature, which is characteristic of semiconductors.

- the decrease in the resistance reflects an increase in the density of free charge carriers: the higher the sample temperature, the greater the number of mobile free electrons in the conduction band (for a n-type semiconductor) or mobile holes in the valence band (for a p-type semiconductor).

- FIGS. 5 a - 5 d The method illustrated in FIGS. 5 a - 5 d has been demonstrated using a one centimeter square integrated circuit chip with 41-125 ⁇ m solder bumps on 250 ⁇ m centers along one edge. This chip was mounted perpendicular to a heat sink. Prior to assembly, the first chip was coated with a bonding layer in the form of a rosin-based flux to provide enough tack to hold the chip in position during the reflow process. The assembly was then reflowed in a nitrogen-filled infrared belt furnace.

- FIG. 10 shows a schematic diagram of such an organic TFT structure with top source and drain contacts, comprising a Si wafer 55 that serves as a gate contact, a SiO 2 insulating layer 56 , an SCTCF 57 , and gold source and drain contacts 58 .

- the procedure of depositing contacts consisted of the following steps: (i) cutting a Si/SiO 2 wafer covered with SCTCF to the required size; (ii) placing a mask (a mechanical mask was glued to the sample surface using Aquaricum silicone gel); (iii) covering the sample surface with gold.

- the last stage was performed using an NRC/Varian Model 3117 Thermal Evaporator equipped with a TM-350 thickness monitor (MAXTEC Inc.). The device was operated at a working pressure inside the evaporator of 10 ⁇ 6 -10 ⁇ 7 Torr and an evaporator current of 150 A.

- the typical contact layer thickness was ⁇ 50 nm. All processing steps were visually controlled using a NIKON Eclipse L200 microscope.

- the bottom contacts were made using a photolithographic method.

- the contact pattern was obtained in a Karl Suss MJB 3 setup.

- the contacts were deposited in a Temescal VES-2550 electron beam evaporator with an INFICTION IC/5 deposition controller. Covering with Sio 2 layer was performed using an Airco Temescal CV-8 electron beam evaporator with an INFICTION XTC/2 deposition controller.

- FIG. 11 shows a schematic diagram of the TFT structure with bottom source and drain contacts comprising a 500 ⁇ m thick Si wafer 61 which also served as the gate contact, a 200 nm thick insulating Sio 2 layer 62 , an SCTCF 63 , a 2.5 nm thick titanium layer 64 for better adhesion of gold, 50 nm thick gold source and drain contacts 65 , and a 800 nm thick protecting SiO 2 layer 66 .

- the contacts were deposited perpendicular and parallel to the film coating direction. The samples with different channel lengths and channel widths are available.

Abstract

Description

- This application claims the benefit of, and priority to, of U.S. provisional patent application Ser. No. 60/152,256 filed on Oct. 17, 2003, entitled “Three-Dimensional Integrated Circuit with Integrated Heat Sinks”, the entire disclosure of which is incorporated herein by reference.

- The present invention relates to a three-dimensional integrated circuit incorporating an integrated heat sink for dissipating heat produced by the integrated semiconductor devices mounted thereon.

- Conventional ICs are formed on the surface of a silicon substrate. A high integration is achieved through enlarging the chip area and employing a discrete approach, which implies making each individual element small and each wiring fine. The discrete approach has limitations in wafer process technology. Accordingly, three-dimensional ICs have been proposed.

- However, the dissipation of heat generated by the integrated components becomes a problem in three-dimensional integrated circuits. To function appropriately, each component should be kept at or below a preset tolerable operating temperature In particular, memory devices running at a high transfer rate produce heat during operation and the integrated circuit rapidly heats up. Without proper heat dissipation, the IC may overheat and malfunction.

- In the general case, a heat sink is used for dissipating heat produced by components in an integrated circuit. IC. The heat sink has to be in good thermal contact with each component and exposed to the surrounds to maximize heat dissipation. In a three-dimensional circuit it is difficult to provide sufficient exposure of the heat sink to the surrounds.

- It is an object of the present invention to provide a three-dimensional integrated circuit with improved heat dissipation.

- The disclosed invention represents a three-dimensional integrated circuit comprising a heat sink and a set of discrete integrated circuits arranged one above another and system of integrated heat sinks for conducting heat from the integrated circuits to the heat sink. Each of said discrete integrated circuits has a heat-conducting substrate and functional elements formed on front and/or rear substrate surface, wherein at least one of the functional elements is a heat-generating element. The integrated heat sinks are in thermal contact both with at least one of said substrates and with the heat sink. In said three-dimensional integrated circuit the widths, lengths, thicknesses and thermal conductivities of the substrates of discrete integrated circuits, as well as the number, cross sectional areas, lengths, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the three-dimensional integrated circuit does not exceed a preset tolerable operation temperature determined for previously established intensities of said functional heat-generating elements and their known positions in the three-dimensional integrated circuit.

- Another aspect of the present invention is a monolithic three-dimensional integrated circuit comprising a heat sink and a monolithic multilayer structure representing a system of unit integrated circuits stacked one above another. This monolithic multilayer structure is mounted on said heat sink. Each of said unit integrated circuits comprises a heat-conducting substrate having front surface and rear surface facing the heat sink. Each of these unit integrated circuits comprises a conducting wiring pattern formed on the front substrate surface, and functional elements mounted on front substrate surface and connected to the wiring pattern. One or more of these elements is a heat-generating element. Each unit integrated circuit is provided with a protective insulating layer, formed above said wiring pattern and said functional elements, and a planarization layer possessing a flat surface. This flat surface of the planarization layer, which is most distant from the front surface of the substrate, serves a base for the subsequent unit integrated circuit of said stacked system. Said three-dimensional monolithic integrated circuit also contains a system of integrated heat sinks. Each integrated heat sink is in thermal contact with said heat sink and penetrates into the monolithic multilayer structure, thus providing thermal contact with at least one substrate of said unit integrated circuits. In this monolithic three-dimensional integrated circuit, the substrate thicknesses and thermal conductivities, as well as the number, cross sectional areas, lengths, arrangement, and thermal conductivities of said integrated heat sinks, are selected so as to ensure that the temperature in any region of the three-dimensional monolithic integrated circuit would not exceed a preset tolerable operation temperature determined for preliminarily established intensities of the said functional heat-generating elements and their known positions in the three-dimensional monolithic integrated circuit.

- Other objects and advantages of the present invention will become apparent upon reading the detailed description of the invention, and upon reference to the drawings, in which:

-

FIG. 1 a is a schematic diagram of a three-dimensional integrated circuit representing a system of several discrete integrated circuits. -

FIG. 1 b is a sectional view of the integrated circuit ofFIG. 1 a taken along the line A-A. -

FIG. 2 shows the main types of electrically conducting elements for connecting to neighboring discrete integrated circuits in a three-dimensional integrated circuit. -

FIG. 3 shows an example of electrical connections between discrete integrated circuits in a three-dimensional integrated circuit via electrically conducting elements of various types. -

FIG. 4 shows an axonometric image of a system of substrates, integrated heat sinks, and a heat sink according to the present invention. -

FIGS. 5 a-5 d are cross-sections of arched solder joint with pads according to the present invention, during intermediate fabrication steps. -

FIG. 6 is a schematic diagram of a three-dimensional integrated circuit with integrated heat sinks according to the present invention, in which thermal contacts are obtained with the use of arched solder joints. -

FIGS. 7 a -7 b show schematic diagrams of the arched solder joints with dimensions according to the present invention. -

FIG. 8 is a schematic diagram of a three-dimensional monolithic integrated circuit according to the present invention. -

FIG. 9 shows the typical temperature dependence of resistance of an semiconductor thin crystal film sample. -

FIG. 10 shows a thin-film transistor structure with top source and drain contacts. -