CN102439532A - 超高速和非超高速usb装置的同步网络 - Google Patents

超高速和非超高速usb装置的同步网络 Download PDFInfo

- Publication number

- CN102439532A CN102439532A CN2010800219729A CN201080021972A CN102439532A CN 102439532 A CN102439532 A CN 102439532A CN 2010800219729 A CN2010800219729 A CN 2010800219729A CN 201080021972 A CN201080021972 A CN 201080021972A CN 102439532 A CN102439532 A CN 102439532A

- Authority

- CN

- China

- Prior art keywords

- hypervelocity

- usb

- usb device

- time

- local clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4204—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus

- G06F13/4221—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being an input/output bus, e.g. ISA bus, EISA bus, PCI bus, SCSI bus

- G06F13/423—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being an input/output bus, e.g. ISA bus, EISA bus, PCI bus, SCSI bus with synchronous protocol

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4022—Coupling between buses using switching circuits, e.g. switching matrix, connection or expansion network

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/08—Clock generators with changeable or programmable clock frequency

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/12—Synchronisation of different clock signals provided by a plurality of clock generators

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/3003—Monitoring arrangements specially adapted to the computing system or computing system component being monitored

- G06F11/3027—Monitoring arrangements specially adapted to the computing system or computing system component being monitored where the computing system component is a bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/10—Program control for peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4027—Coupling between buses using bus bridges

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4027—Coupling between buses using bus bridges

- G06F13/405—Coupling between buses using bus bridges where the bridge performs a synchronising function

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0042—Universal serial bus [USB]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

- H04L7/08—Speed or phase control by synchronisation signals the synchronisation signals recurring cyclically

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- Computing Systems (AREA)

- Quality & Reliability (AREA)

- Information Transfer Systems (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

Abstract

一种使多个超高速USB装置和多个非超高速USB装置的运行同步的方法,该方法包括:为所述多个超高速USB装置的每一个建立超高速同步信道;为所述多个非超高速USB装置的每一个建立非超高速同步信道;使所述多个超高速USB装置的每一个的各个本地时钟同步;使所述多个非超高速USB装置的每一个的各个本地时钟同步;和使所述超高速同步信道和非超高速同步信道同步,从而使得所述超高速和非超高速装置能同步地运行。

Description

技术领域

本发明涉及一种提供基于版本3的通用串行总线(USB)架构(或USB3.0)的、具有连通性的同步和时序系统的方法和设备,该系统具体地但决不是排它地用于提供在本地环境或分布式方案中以必要的任意程度同步的测试和测量设备、仪器接口和过程控制设备的时钟、数据采集以及自动化和控制。

背景技术

版本2.0的USB规范和包括版本2.0的USB规范旨在以开放的架构促进来自不同厂商的装置的互操作。超高速USB数据利用采用两条导线的信号电平之差的形式的差分信令(即其中这两条导线传送信息)来编码。USB 2.0规范旨在作为对PC架构、跨越便携的环境、台式和家用环境的增强。

不过,USB是用户集中的,因此USB 2.0规范缺少用于使装置同步达到任意高精度的机制。几种提案曾尝试去解决这种和其它的不足。例如,第6,343,364号美国专利(Leydier等人)公开了一种对被引导到智能卡读取器的USB通信流进行频率锁定的实施例。该文件披露了与USB SYNC和包ID流比较的本地、自由运行的时钟;其周期被更新以匹配这个频率,从而产生1.5MHz的标称频率的本地时钟。这提供了足以将智能卡信息读取到主机PC内的同步程度,但这种方法面向智能卡读取器,因而不能解决装置间的同步。

WO 2007/092997(Foster等人)公开了允许在USB装置上产生精确的时钟频率、而不考虑主机PC中时钟的精确性的同步USB装置。USB SOF包被USB装置解码,并被处理作为时钟载波信号,而不是充当时钟基准。

载波信号,一旦从USB通信流被解码,将与比例因子(scaling factor)结合以产生同步信息,从而合成时钟频率精确控制的本地时钟信号。以这种方式,相比载波信号的有点不确定的频率,本地时钟信号的频率可更加精确。

据说这种布置能够产生达到任意高频的本地时钟信号,例如几十兆赫的时钟频率,因此能够确保连接至给定USB的每个装置的本地时钟在频率上同步。第10/620,769号美国申请也披露了一种方法和设备,从而通过测量信号从主机到每个装置的传播时间并在每个USB装置上提供时钟相位补偿以进一步使多个本地时钟在相位上同步。

美国专利申请12/279,328(Foster等人)披露了多个USB装置的本地时钟与从另一个接口接收的时间基准同步。在一个实施方式中,USB装置包含本地时钟,该本地时钟与使用IEEE-1588协议经过以太网而外部提供的时间标记同步。在又一个实施方式中,USB装置的时钟与来自全球定位系统(GPS)同步化时钟的时间基准同步。

所有上面的系统都适用于常规的USB 2.0,并同样地限于几个领域中。由于设备响应超时,USB 2.0在范围上被限制。这是USB主机控制器响应来自所述USB主机控制器的请求而分配从给定的USB装置接收信号的时间窗。因此USB 2.0的物理长度接近25m。

2008年11月发布了USB 3.0规范,其也关注于消费者应用。USB 3.0规范对USB架构做出了显著的改变。具体来说,上述的背景技术同步配置将不适用于新的5Gb/s协议(称作“超高速USB”),因为该协议废除了用于SOF包的广播机制。

USB 3.0在同一连接电缆上限定了两个并行且独立的USB总线。首先,USB 2.0总线(对于后面的兼容性)保持不变并提供低速(1.5Mb/s)、全速(12Mb/s)和高速(480Mb/s)协议。第二总线—对于5Gb/s通信流—提供超高速USB。除了总线到给定USB装置的操作是互斥的之外,这些总线独立地工作。也就是说,如果超高速连接是可能的,则USB 2.0总线就与该装置断开。

在图1中以10来示意性描述USB 3.0的双总线架构。包括USB主机控制器14的个人计算机12通过第一USB 3.0从属电缆(compliant cable)18被连接到USB 3.0集线器16;USB 3.0装置20通过第二USB 3.0从属电缆24被连接到USB 3.0集线器16的下游端口22。

USB主机控制器14包括USB 2.0主机26和超高速主机28两者。这两个主机26、28彼此独立,且每个主机26、28能够连接多达127个装置(包括集线器)。USB 3.0从属电缆为复合电缆,包含USB 2.0从属电缆和一串能够传送超高速信号的屏蔽导线。于是,USB 3.0从属电缆18包括USB 2.0从属电缆30和屏蔽导线32。

USB 3.0集线器16包含USB 2.0集线器功能元件34和超高速集线器功能元件36,每个功能元件通过复合电缆18都被直接地连接到其各自的主机26、28。USB 3.0装置20包含USB 2.0装置功能元件38和超高速装置功能元件40,每个功能元件通过复合电缆24都向后连接到其各自的USB 3.0集线器16的集线器功能元件34、36。

在列举的USB 3.0装置20处,超高速主机28针对超高速装置功能元件(40)的存在进行检查。如果发现超高速装置,则建立连接。如果未发现超高速装置(如仅将USB 2.0装置连接到端口22的情况),则USB 2.0主机26针对USB 2.0装置功能元件(38)在装置20中的存在进行检查。一旦主机控制器14确定哪个装置功能元件被连接,则其指示USB 3.0集线器16对应于是USB 2.0装置功能元件38还是超高速装置功能元件40被附接而仅仅启动下游端口22的通信。这意味着在任意一个时间两个并行总线中仅仅一个与例如USB 3.0装置20的终端装置处于操作状态。

此外,超高速USB具有不同于USB 2.0总线的架构。由于高比特率,相当高速的通信系统消耗了大量的能量。超高速USB的设计要求是较低的功耗以延长用户装置的电池寿命。这已导致USB 2.0的先前广播设计发生改变:超高速不是广播总线,而是将通信包指向系统中特定的节点,并切断空闲链路上的通信。

这严重影响了例如第12/279,328号美国专利申请的同步配置的任意扩展,该美国专利申请的用于同步装置的方法和设备是基于在总线上被传递至每个装置的广播时钟载波信号,该信号不适于超高速USB。

超高速集线器功能元件起着装置到主机(或上游端口)和主机到装置(或下游端口)的作用。这意味着超高速集线器功能元件起着缓冲和调度其下游端口上的交易的作用,而不仅仅起着中继器的作用。同样地,超高速集线器功能元件也起着调度上游端口上的交易的作用。因此,负荷重的集线器功能元件会在通过系统传输包时增加显著的非确定性延迟。这也阻止了例如第12/279,328号美国专利申请的USB 2.0同步配置在超高速USB上操作的使用。

USB 2.0不成熟的等时同步在USB 3.0规范中显著得到了改善。打开主机控制器和USB装置之间的等时通信管道保证在每个服务间隔中通信管道的固定带宽分配。USB 3.0的等时协议包含所谓的等时时间戳包(ITP),该时间戳包以稍微规则的间隔被发送到每个等时端点,并且包含在主机控制器的时域中由USB主机物理层(Phy)进行的ITP交易的开始的时间戳。该等时时间戳包精确到大约25ns。超高速USB切断空闲链路以保存能量,但为了接收等时时间戳包,链路必须是有源的。因此,主机控制器必须保证在等时时间戳包的传输之前到装置的所有链路处于完全有源模式(称作电源状态U0)。

遗憾的是,等时时间戳包会在沿着USB网络的传播中被延迟。USB 3.0也未提供确定包在超高速USB中的传播时间的方法,因此没有方法精确地知道在不同USB装置上的时域之间的相位关系。期望几百纳秒的相位差为最佳情况,利用超高速USB使其对于仪器化或其他精度时序要求是不切合实际的。

第5,566,180号美国专利(Eidson等人)公开了一种同步时钟的方法,其中通信网络上的一串装置互相传送它们的本地时间,且由消息群确定网络传播时间。Eidson的进一步公开(第6,278,710、6,665,316、6,741,952和7,251,199号美国专利)扩展了这种概念,但仅仅致力于其中同步消息的恒流经由因特网在分布式仪器网络的每个节点之间传递的同步配置。这样连续的发送消息消耗了带宽,并且将可能的同步化的精确度限制到在点对点的布置中为几百纳米秒和在常规的交换式子网中为更低的精确度(通常微秒)。

应当理解的是,在本公开中术语“时钟信号”和“同步”用于指代时钟信号、触发信号、延迟补偿信息以及传播时间测量信息。还应当理解的是,在本公开中“时间的概念”用于表示出现时间(epoch)或“实际时间”,也可用于指代时钟信号和相关出现时间的结合。

发明内容

本发明的一般目的是根据USB3规范实现多个USB装置的精确性同步,达到预定义的最大值。

具体地,在第一广义方面,本方面提供一种使多个超高速USB装置和多个非超高速USB装置的运行同步的方法,包括:

为所述多个超高速USB装置的每一个建立超高速同步信道;

为所述多个非超高速USB装置的每一个建立非超高速同步信道;

使所述多个超高速USB装置的每一个的各个本地时钟同步;

使所述多个非超高速USB装置的每一个的各个本地时钟同步;和

使所述超高速同步信道和非超高速同步信道同步,从而所述超高速和非超高速装置能同步地运行。

因此,本发明允许超高速连接的USB装置和非超高速连接的USB装置在公共USB上的同步运行。

因此,该方法允许例如超高速等时时序与非超高速(或高速)SOF时序的同步。

在一个实施方式中,该方法包括利用等时传送方法使所述超高速USB装置的每一个的所述本地时钟谐振或锁频,所述等时传送方法包括:

在所述主机控制器和所述各个超高速USB装置之间打开至少一个等时通信管道;

保证所述各个超高速USB装置处于链路状态U0,以准备接收等时时间戳包(ITP);

所述主机控制器将多个多播传送周期性等时时间戳包发送到所述等时端点的每一个;

将所述各个超高速USB装置的各个本地时钟锁定为来自所述周期性等时时间戳包(ITP)的信息;

从而将所述周期性等时时间戳包内包含的时间戳用作基准时间,来使所述各个超高速USB装置的各个本地时钟与所述主机控制器的时域谐振,并且利用所述等时时间戳包从所述主机控制器到所述各个超高速USB装置的传播时间,来使所述各个本地时钟同步或相位对准。

该方法可以进一步包括确定和补偿所述各个超高速USB装置的所述各个本地时钟由于所述等时时间戳包从所述主机控制器或USB集线器到所述各个超高速USB装置的相对传播时间所引起的相位误差。

在某些实施方式中,该方法包括另外利用不用的非超高速信号导线使所述超高速USB装置的每一个的所述各个本地时钟谐振或锁频,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述超高速USB装置的上游端口处,多路分离来自D+/D-信令线路的同步信息;和

将所述各个超高速USB装置的所述各个本地时钟锁定到所述同步信息。

所述同步信息可包括触发信号、时钟信号和时钟相位信息。

根据该实施方式,该方法可以进一步包括确定和补偿所述各个超高速USB装置的所述各个本地时钟由于所述同步信息从所述主机控制器或USB集线器到所述各个超高速USB装置的每一个的相对传播时间所引起的相位误差。

在另一个实施方式中,使所述非超高速USB装置的各个本地时钟同步包括:

监控在所述各个非超高速USB装置本地的USB数据通信流;

对来自所述USB数据流的多个周期性信号结构解码;

将所述非超高速USB装置的所述各个本地时钟锁定到来自所述周期性信号结构的信息;

从而将所述周期性信号结构用作基准时间,来使所述非超高速USB装置的所述各个本地时钟与所述主机控制器的时域谐振,并且利用所述周期性信号结构从所述主机控制器到所述各个非超高速USB装置的各个传播时间,来使所述本地时钟同步或相位对准。

该方法还可以进一步包括确定和补偿所述非超高速USB装置的所述各个本地时钟由于所述周期性信号结构从所述主机控制器或USB集线器到所述各个非超高速USB装置的各个相对传播时间所引起的相位误差。

所述周期性信号结构可以包括USB帧起始包。

在具体实施方式中,使所述超高速同步信道和非超高速同步信道同步包括:

在所述非超高速同步信道的时域中,确定各个第一等时数据包和等时时间戳包从所述主机控制器到所述各个超高速USB装置的每一个的各自传输时间;

向所述主机控制器报告所述各自传输时间;和

所述主机控制器在所述超高速USB装置的各个时域和所述非超高速USB装置的时域之间创建映射;和

使所述超高速USB装置的各个USB装置功能电路的多个运行或事件的每一个的各个本地时间与所述主机控制器的时域匹配;

从而所述运行或事件的每一个能被反向映射到所述非超高速USB装置的时域。

可规定等时传送以特定的USB帧(或微帧)开始。上述的这个方面的方法可包括在非超高速同步信道的时域中确定多个等时时间戳包到多个超高速USB装置的每一个的传输时间(时间戳),从而提供更多关于时域之间的映射的信息,这对本领域技术人员来说是显然的。

多个非超高速USB装置可包含有线非超高速USB装置或无线USB装置,这对本领域技术人员来说也是显然的。在这种情况下,基于帧起始的同步方案(例如上述背景技术的那些)将可同样地适用,并且无线USB可用作本发明中披露的任意非超高速同步信道的同步信道。

超高速USB装置的本地时钟的同步或相位对准可通过利用USB装置特征设置等时延迟(Set Isochronous Delay)或通过调节所述本地时钟的相位的任意其它方法而实现。

根据第二广义方面,本发明提供一种使USB网络中多个超高速USB装置和非超高速USB装置的各个本地时钟同步的方法,该USB网络包括多个USB集线器、一个以上的超高速USB装置和一个以上的非超高速USB装置,该方法包括:

确定所述USB网络的连接布局;

在所述USB网络的最上方USB集线器处建立非超高速同步信道;

在所述USB网络的每个网络支路中识别在其各个子网络中不包含任何非超高速USB装置的各个最高USB集线器端口,每个各个最高USB集线器端口被设置于每个所述网络支路的对应的最高USB集线器中;

建立从所述各个最高USB集线器端口到附接到其上的每个所述超高速USB装置的各个超高速同步信道;

使所述各个最高USB集线器的各个本地时钟通过它们各自的上游非超高速同步信道同步;

使所述非超高速USB装置的所述本地时钟通过各自的非超高速同步信道同步;和

使所述各个超高速USB装置的所述本地时钟通过所述各自的超高速同步信道同步;

从而使所述超高速同步信道与在其各个网络支路中对应的各个所述最高USB集线器的时间概念同步,并且使所述最高USB集线器的各个本地时钟与非超高速同步信道同步。

在一个实施方式中,该方法包括另外利用不用的非超高速信号导线使所述超高速USB装置的所述各个本地时钟的每一个谐振或锁频,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述超高速USB装置的上游端口处,多路分离来自D+和D-信令线路的同步信息;和

将所述各个超高速USB装置的所述各个本地时钟锁定到所述同步信息。

该方法还可包括确定和补偿所述本地时钟由于所述同步信息从所述USB主机控制器或USB集线器到所述多个USB装置的每一个的相对传播时间所引起的相位误差。

附加的同步信息通常包括计时、绝对时间基准和触发信号。

因此,该方法允许通过USB 2.0导线为超高速USB装置提供同步信道(包括同步计时、绝对时间基准和触发信号)。同步信道提供了主要用于同步USB的范围的机制。背景技术系统依赖于帧起始(SOF)包在高速USB 2.0上的传输,但该系统的范围有限。USB 2.0标准定义了经过USB集线器具有5层扩展的分层星型拓扑,且每层最大的电缆长度为5m,因此总的分布范围为25m。这是由于在USB 2.0协议下用于每个装置的有限的通信窗口,在其中对于所有业务都具有通信超时时段,并且主机控制器必须在从主机请求传输起的特定时间段内从USB装置接收应答。根据本发明的这个方面,利用USB2SOF包实现不了同步。相反地,使到USB装置的USB 2.0通信失效,且将专用的同步信息多路复用到断开的USB2导线上。关于USB3的超时限制是提供大约几十公里的物理范围的毫秒级。出于所有意图和目的,这种同步信道的物理范围仅由传输层的选择来确定。

USB电缆在通向多个USB装置中每一个的下游通路中可包括多个电缆段和多个USB集线器。

信令线路通常采用导电对的形式,并且可包括铜电缆(其符合USB 3.0规范)。可替代地,信令线路可包括具有铜导线和光纤导线的混合电缆或只是光纤导线。

其它同步信息也可经USB D+/D-数据信令线路而被传输,这对本领域技术人员来说是显然的,且该实施方式不限制同步信息的范围。

在一个实施方式中,上游连接点是含有用于USB扩展的多个连接点的USB集线器。优选地,USB集线器包含精确定时基准或同步于外部精确定时基准的本地时钟。

在另一个实施方式中,该方法包括由在USB集线器处的电路产生同步信息。该同步信息可由在USB集线器处的电路从外部源接收,例如全球定位系统(GPS)参考时钟源、原子钟、以太网(例如采用网络时间协议(NTP)或IEEE-1588精确时间协议(PTP)的形式)、无线同步机制、小型PCI仪器系统、PXI仪器系统、VXI仪器系统或另一个仪器系统。以这种方式,同步信道能够通过分布很广的网络提供精确到外部基准时钟的精确定时基准。

在一个实施方式中,同步桥(在多个总线之间的桥接)包括在个人计算机系统内使用的插入式电路板。在又一个实施方式中,所述同步桥包括用于诸如小型PCI、PXI、PXI-express、VXI、VME之类的仪器系统或其它仪器系统的插入式电路板。在PXI和PXI-express的情况中最为特别地是,所述同步桥优选地被用于槽1时序控制器卡槽以通过所述PXI或PXI-express仪器机箱实现同步。此外,所述同步桥可包括使所述超高速USB与无线USB网络或利用各种协议的另一类型网络的无线网络同步的电路。

在另一个实施方式中,所述同步桥包括家庭娱乐系统,从而音频流和视频流被同步,且通过最显著利用精确时间协议(PTP)或IEEE-1588的多个总线,例如超高速USB和以太网被分布。在这种情况下,例如用于家庭影院或游戏应用的视听信息被所述桥解码(或也可被另一个部件解码且被传送到所述桥),以通过多个同步网络进行传递。虽然对本领域技术人员来说其它实施方式是显然的,但在优选实施方式中,视频流通过与传输所述音频流的所述以太网同步的所述超高速USB被传递。

同步信息可以时域多路复用的方式而被分布,其中同步信息的不同组成部分在同步信道的总通信带宽内占据它们自己各自的时隙。例如,周期性时钟载波信号可占据第一时隙,绝对时间基准信号占据第二时隙以及触发信号占据第三时隙。

同步信息可以采用通过D+/D-数据信令线路的差分信令的形式。

可替代地,该方法可包括由D+和D-数据信令线路上的单端信令提供同步信息。在该实施方式中,该方法可包括通过数据信令线路分布同步信息。例如,该方法可包括经第一数据信令线路传输时钟载波信号,并且经第二数据信令线路传输绝对时间基准信号和触发信号。用于经数据信令线路传送同步信息的其它配置是可能的,这对本领域技术人员来说是显然的。

在一个实施方式中,所述方法包括使所述非超高速USB装置的所述本地时钟同步包括:

监控在所述非超高速USB装置的每一个本地的USB数据通信流;

对来自所述USB数据流的多个周期性信号结构解码;

将所述非超高速USB装置的所述各个本地时钟锁定到来自所述周期性信号结构的信息;

从而将所述周期性信号结构(优选为USB帧起始包)用作基准时间,来使所述非超高速USB装置的所述各个本地时钟与所述主机控制器的时域谐振,并且利用所述周期性信号结构自所述主机控制器的相对传播时间而使所述非超高速USB装置的所述本地时钟同步或相位对准。

所述周期性信号结构可包括USB帧起始包。

该方法可进一步包括确定和补偿所述非超高速USB装置的所述本地时钟由于所述周期性信号结构从所述USB主机控制器或USB集线器到所述各个非超高速USB装置的相对传播时间所引起的相位误差。

在具体实施方式中,该方法进一步包括:

使所述USB集线器和所述非超高速USB装置的所述各个本地时钟锁定到或同步于基本相同的频率;

测量非超高速信号从所述最上方USB集线器到所述最高USB集线器和非超高速USB装置的每一个的各个往返传播时间;

确定非超高速信号到所述USB集线器和非超高速USB装置的每一个的各个下游传播时间或相对下游传播时间;

同步或调节所述USB集线器的所述本地时钟的每一个的相位和包含在所述非超高速同步信道中的所述非超高速USB装置的所述本地时钟的每一个的相位;和

为所述USB装置的每一个提供公共的时间概念。

该方法可包括另外利用不用的非超高速信号导线使所述超高速USB装置的所述各个本地时钟谐振于或锁频到所述最高USB集线器,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述各个超高速USB装置的上游端口处,多路分离来自D+/D-信令线路的同步信息;

将所述超高速USB装置的所述各个本地时钟锁定到所述同步信息,

其中,所述附加的同步信息由所述最上方USB集线器的所述本地时钟产生,从而使所述超高速USB装置的所述各个本地时钟与所述非超高速同步信道的时间概念同步。

该方法可进一步包括确定和补偿所述超高速USB装置的所述本地时钟由于所述附加的同步信息从所述各个最高USB集线器到所述各个超高速USB装置的相对传播时间所引起的相位误差。

根据第三广义方面,本发明提供一种用于在多个同步的超高速USB装置中补偿电缆传播时间引起的相位偏移的方法,包括:

建立从USB主机到各个超高速USB装置的各个超高速通信信道连接,每个连接包括各个USB电缆;

在各个USB电缆的上游连接点处,使各个USB电缆的USB2D+/D-数据信令线路失效或断开;

在上游连接点处,将附加的同步信息(例如计时、绝对时间基准和触发信号)多路复用到D+/D-信令线路上;

在USB装置的每一个处,多路分离来自D+/D-数据信令线路的同步信息;

将D+/D-数据信令线路上的传播定时信号传输到USB装置;

从USB装置接收作为传播定时信号的响应而产生的响应信号并对其解码;

测量在每个USB装置的传播定时信号的传输和响应信号的接收之间的各个时间间隔;

确定每个USB装置的相对下游传播时间;

指定所述USB装置的一个作为时态基准装置(temporal reference device);

确定在时态基准装置和除时态基准装置之外的每一个USB装置的相对下游传播时间之间的各个差;

使在USB装置本地的各个时钟在频率和相位上谐振于或锁定到同步信息;

确定本地时钟相对于时态基准USB装置的本地时钟的各个相位;

确定为了大致同相地放置本地时钟所需的本地时钟的各个时态调整或相位偏移(注意并非所有的USB装置可被确定以要求时态调整或相位偏移);

将时态调整或相位偏移(例如自USB主机)传输到各个USB装置(注意这可意味着如果根据前面步骤中的需要确定没有时态调整或相位偏移,则一些USB装置可不接收时态调整或相位偏移);和

根据传输到其上的各个时态调整或相位偏移而对各个本地时钟进行相位调节。

因此,这方面在D+/D-数据信令线路上提供了时间-延迟-循环-返回信号。

此外,该时态调整对于针对所有同步信息补偿电缆传播时间是有效的。因此为所有同步信息提供一般的相位调整允许每个USB装置的计时信号、绝对时间基准信号、触发信号和任意其它形式的同步信息的同步。

每个连接可在通向各个USB装置的下游通路中包括多个电缆段和多个USB集线器。

时间间隔包括三个分量:下游传播时间、上游传播时间和在各个USB装置中由于产生对传播计时信号的响应而引起的反应时间。通过USB电缆的信号传播时间通常可视为对称的,并且反应时间对于相同特性的所有USB装置应该具有均匀的值。因此预期信号传播时间正好为每个USB装置的时间间隔的一半加上反应时间所引起的某一恒定值。结果,该恒定反应时间在确定相对下游传播时间时被抵消。

根据第四广义方面,本发明提供一种用于使USB网络中一个以上的超高速USB装置和一个以上的非超高速USB装置同步的设备,包括:

具有超高速USB上游端口的USB集线器;

多个超高速USB下游端口;

适于执行USB 3.0集线器功能的USB集线器功能电路,该功能提供到所述上游端口和到所述多个下游端口的连接;和

至少一个USB装置功能电路,所述USB装置功能电路被连接至所述下游端口中的一个;

解码电路,用于在所述上游端口处对来自非超高速USB数据流的周期性信号结构解码;

谐振器电路,适于使所述设备的本地时钟与所述周期性信号结构谐振;

适于使所述本地时钟与外部的时间概念(即该设备之外)同步的同步器(例如采用同步电路的形式);

适于产生所述本地时钟所参考的附加的同步信息(例如计时、绝对时间基准和触发信号)的电路;和

能操作以选择性地使所述设备的每个下游USB端口的下游非超高速D+/D-数据信令线路从它们各个USB集线器功能元件下游端口失效的电路;

多路复用器(例如采用多路复用电路的形式),用于在所述多个下游USB连接器的每一个处将来自所述本地时钟的所述附加的同步信息多路复用到所述下游D+/D-信令线路上,能操作以将所述非超高速USB D+/D-信号引导向具有附接的非超高速装置的任意下游USB连接器,并将所述附加的同步信息引导向具有附接的超高速USB装置的任意所述下游USB连接器;和

定时器(例如采用定时电路的形式),适于确定信号从所述设备到一个以上附接的下游USB装置的各个往返时间间隔;

其中,所述USB装置功能电路适于将由定时器确定的所述往返时间间隔传输到所述USB网络的USB主机控制器。

因此,提供了一种用于使混合的超高速/非超高速网络同步的设备(例如采用USB集线器的形式),该设备容许同步计时并提供绝对时间基准和触发信号。USB主机控制器通常位于该设备之外,但在某一实施方式中,该设备包括USB主机控制器。例如,该设备—包括USB主机控制器—可被制造在单芯片上。

因此,本发明仅利用单个电缆即可使多个超高速USB装置的每一个的本地时钟同步。这涉及利用符合USB3的装置支座以允许和其它常规的USB电缆和装置一起无缝使用。USB 3.0规范限定在进行到USB 3.0装置的超高速连接时,集线器使到该装置的USB 2.0信号失效。在进行超高速装置连接时,该公开的仪器总线架构利用了在USB 3.0电缆中不用的信号线。这同样可应用于任何要求同步信道和USB超高速连接的应用中。

该设备可包括用于控制多路复用器的状态的电路。

针对超高速和非超高速下游装置,定时器可适于采用不同的测量技术。在一个实施方式中,定时器测量在每个所附接的非超高速USB装置的上游端口之间的往返时间。根据该实施方式,该定时器测量从用于产生定时信号的电路到每个所附接的超高速USB装置以及返回的往返时间。该往返时间可根据任何合适的方法来测量,包括这里公开的任何一种往返测量方法。

所述USB装置功能电路可适于执行非超高速装置功能。

在一个实施方式中,所述USB装置功能电路适于执行超高速装置功能。

在一个实施方式中,所述外部时间概念可由所述USB主机控制器提供。

所述同步器还可适于使所述本地时钟与外部接口谐振。

在一个实施方式中,该设备适于从所述外部接口接收所述外部时间概念。

所述外部接口可包括GPS时钟、PXI机箱槽1时序控制器、以太网接口、IEEE-1588精确时间协议以太网(Precision Time Protocol Ethernet)、网络时间协议以太网(Network Time Protocol Ethernet)、原子钟或靶场间仪器组(Inter-RangeInstrumentation Group(IRIG))接口中的任意一个或多个。

在具体实施方式中,该设备进一步包括USB主机控制器功能元件,其适于连接到所述USB集线器的所述上游端口。

在一个实施方式中,所述谐振器电路包括:

用于观测在任意附接的USB装置的各个连接点或下游端口本地的USB数据流的电路;

用于对来自所述USB数据流的周期性信号结构解码的电路;

用于对应对来自所述USB数据流的周期性数据结构解码而在所述设备本地产生事件信号的电路;

用于相对于所述事件信号的频率锁定所述本地时钟的频率的电路。

在具体实施方式中,用于观测USB数据流的电路位于上游端口处。

此外,该设备可被布置为同步桥。在该配置中,本地时钟电路可与外部基准时钟和自USB环境外部提供的时间概念同步。该设备还可包括具有时钟的USB主机控制器和允许主机控制器的时钟与外部基准时钟同步的电路。

在该实施方式中,外部基准时钟和相关联的时间概念(即外部时间源)可包括全球定位系统(GPS)基准时钟信号;原子钟信号;同步的USB;以太网时间码信号,例如但不限于IEEE-1588精确时间协议(PTP)基准时间信号、网络时间协议(NTP)时间信号或其它以太网时间基准;靶场间仪器组(IRIG)基准时间信号或任意其它基准时间信号。该外部时间源可经电缆、光纤、无线机制或其它信号传送或传输机制而被接收。

因此,本发明使超高速连接的USB装置同步于例如经以太网(利用网络时间协议(NTP)、IEEE-1588同步协议或任意其它时间源)连接的装置、经PCI总线或小型PCI总线连接的装置、经PXI(或PXI-express)总线连接的装置、经VXI或VME总线连接的装置、经包括但不限于Zigbee或无线USB的无线机制连接的装置以及通过其它通信总线连接的装置。

非超高速USB装置可为高速或全速装置,并且优选地适于使本地时钟与USB SOF包令牌同步。在一个具体实施方式中,周期性信号结构包括一个以上的OUT令牌、IN令牌、ACK令牌、NAK令牌、STALL令牌、PRE令牌、SOF令牌、SETUP令牌、DATA0令牌、DATA1令牌、或USB数据包中可编程的序列比特模式。

根据第五广义方面,提供一种用于向一个以上超高速连接的USB装置提供同步信号的设备,该设备包括:

包含超高速USB上游端口的USB集线器;和

多个超高速USB下游端口;

时钟或时钟电路;

适于产生所述本地时钟所参考的同步信息的电路;

能操作以将所述同步信息多路复用到选定的一个以上所述下游端口的D+/D-信令线路上,USB装置以超高速USB模式被附接和连接到选定的一个以上所述下游端口。

根据第六广义方面,提供一种使以超高速模式连接的USB装置的时钟与附接到该USB装置的USB集线器的时钟同步的方法,该方法包括:

从所述USB集线器的所述时钟产生同步信息;

将所述同步信息多路复用到所述USB装置所附接到的所述USB集线器的下游端口的不用的D+/D-信令线路上;

使所述USB装置的所述时钟与所述同步信息同步;

从而所述USB装置被连接到主机控制器并通过所述USB集线器利用超高速USB协议与主机控制器通信,并且同时与所述USB集线器的所述时钟的时间概念同步。

所述同步信息可包括所述USB集线器的所述时钟可与其谐振的谐振信息。

在一个实施方式中,所述谐振信息包括周期性信号,而在特定实施方式中,所述同步信息包含所述USB集线器的所述时钟的时间概念。在具体实施方式中,所述同步信息包括一个以上的触发信号。

在一个实施方式中,该方法进一步包括确定从所述USB集线器到所述USB装置的信号传播时间。

根据所述信号传播时间的确定而对所述USB装置的所述时钟相位进行调节。

根据第七广义方面,提供一种使公共USB网络的超高速USB装置和非超高速USB装置的相位同步的方法,包括:

使所述非超高速USB装置的本地时钟相对于周期性帧起始包谐振;

使所述超高速USB装置的本地时钟相对于周期性等时时间戳包谐振;

确定在基本接近所述USB网络的顶部的点和所述非超高速USB装置之间的非超高速传播时间;

确定在基本接近所述USB网络的顶部的点和所述超高速USB装置之间往返的超高速传播时间;

确定所述超高速传播时间和所述非超高速传播时间之间的差;和

根据所述超高速传播时间和所述非超高速传播时间之间的所述差调节所述本地时钟的相位。

所述非超高速传播时间可被确定为例如单向或往返传播时间。

所述超高速传播时间可被确定为例如单向或往返传播时间(后者容易被测量,前者根据后者更容易确定)。应当理解的是,即使根据不同的定义确定了非超高速和超高速传播时间,确定两者之间的差也是简单的问题,例如通过适当地对两个中的一个或另一个加倍或减半。

在一个实施方式中,该方法进一步包括:

使又一非超高速USB装置的本地时钟相对于周期性帧起始包谐振;

确定在基本接近所述USB网络的顶部的点和所述又一非超高速USB装置之间的又一非超高速传播时间;

确定所述超高速传播时间和所述一个非超高速传播时间之间的差;和

根据所述超高速传播时间和又一非超高速传播时间之间的所述差调节所述非超高速USB装置的所述本地时钟的相位。

在一个实施方式中,该方法进一步包括:

使又一超高速USB装置的本地时钟相对于周期性帧起始包谐振;

确定在基本接近所述USB网络的顶部的点和所述又一超高速USB装置之间的又一超高速传播时间;

确定所述又一超高速传播时间和所述非超高速传播时间之间的差;和

根据所述又一超高速传播时间和所述非超高速传播时间之间的所述差调节所述非超高速USB装置的所述本地时钟的相位。

该最后描述的两个实施方式,如果重复采用,则容许使公共USB网络中多个超高速USB装置和/或多个非超高速USB装置相位的同步。

应当注意的是,可以根据适应性和期望来结合本发明的以上每个方面的所有各个特征。

此外,应当注意的是,本发明还提供被布置为执行上述发明的每个方法的设备和系统。

另外,可以用各种方式来实施根据本发明的设备。例如,这种装置可采用位于印刷电路或印刷布线板上、陶瓷基板上或半导线级别即单个硅(或其它半导线材料)芯片处的多个部件的形式配置而成。

附图说明

为了本发明可更加清楚地被确定,现在参照附图,通过实施例描述实施方式,其中:

图1为根据背景技术的USB3的双总线架构的示意图;

图2为根据本发明实施方式的包含超高速和非超高速USB装置的同步USB的示意图;

图3为用于图3的同步USB的超高速和非超高速USB装置的同步的周期性时序信号的相对时序的示意图;

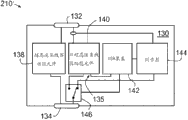

图4A为根据本发明实施方式的USB定时集线器的示意图;

图4B为根据本发明实施方式的同步USB装置的示意图;

图5A为图4A的USB定时集线器的简化版本的具体状态(在其中提供超高速同步信道)的示意图;

图5B为图4A的USB定时集线器的简化版本的具体状态(在其中提供非超高速同步信道)的示意图;

图6为根据本发明实施方式的混合的超高速和非超高速同步USB网络的示意图;以及

图7为图示根据本发明实施方式的同步的超高速和非超高速USB装置对的时序信号的示意图。

具体实施方式

在图2中以70示意性示出根据本发明第一实施方式的设置于个人计算机(PC)72中的同步USB。PC 72包括被连接至包含超高速USB定时集线器78、超高速USB装置80和非超高速USB装置82的网络76的超高速USB主机控制器74。USB主机控制器74通过包括超高速导线86和非超高速导线88的复合USB电缆84而被连接至USB定时集线器78。

USB定时集线器78支撑超高速USB装置80和非超高速USB装置82两者的附接,因此超高速导线86和非超高速导线88两者都传送超高速USB主机控制器74和USB定时集线器78之间的信号。

超高速USB装置80通过包括超高速导线92和非超高速导线94的符合超高速标准的复合USB电缆90而被连接至USB定时集线器78。由于装置USB 80为超高速USB装置,因此USB定时集线器78关闭到导线94的非超高速数据通信流,因而超高速装置80和USB定时集线器78之间的连接仅由超高速导线92提供。非超高速USB装置82通过包括超高速导线98和非超高速导线100的符合超高速标准的复合USB电缆96而被连接至USB定时集线器78。在由非超高速导线100执行到非超高速USB装置82的数据连接时,没有信号通过超高速USB导线98。

在该实施例中,在USB定时集线器78和超高速USB装置80之间的超高速导线92(属于复合USB电缆90的)适于提供超高速同步信道,而在USB定时集线器78和非超高速USB装置82之间的非超高速电缆段100(属于复合USB电缆96的)可以说提供了非超高速同步信道。

根据该实施方式,超高速USB装置80与非超高速USB装置82同步。非超高速USB通信流中的帧与等时超高速时间戳包具有基本恒定的相位关系。图3为经由图2的USB定时集线器78的时序信号通信流的以110表示的示例性时序图的示意图,表示超高速同步信道和非超高速同步信道的时序信号之间的关系。

参照图3,总线间隔112-限定为125μs周期—对于超高速和非超高速总线两者是共同的。为非超高速同步信道的同步所选择的典型周期性信号结构为帧起始(SOF)包,其在总线间隔边界处的每个总线间隔出现一次。在帧起始包(参见图3的上部寄存器)的传输中具有非常严格的容差114:帧起始包必须在总线间隔边界的纳秒内被传输。

通过对比,在等时时间戳包(ITP)窗口(图3的中间寄存器)上超高速同步信道具有非常宽松的容差116。ITP窗口允许ITP在离总线间隔边界8μs的区域内的任何地方都可传输。该导致在等时时间戳包(自各个总线间隔边界120所经历的时间)的传输中产生明显的时序抖动。等时时间戳包(参见图3的下部寄存器)也包含从总线间隔边界到等时时间戳包的传输所经历时间的时间戳。该机制允许所附接的USB装置跟踪主机控制器时间。

然而,在该实施方式中主要使用的两个时间标记具有已知的相位关系,这允许超高速和非超高速同步信道的精确同步。

在另一个实施方式中,本发明提供一种用于同步多个超高速和非超高速信道的系统。图4A为根据该实施方式的超高速USB定时集线器130的示意图。USB定时集线器130具有用于和USB主机控制器通信的上游端口132、多个用于与USB装置通信的下游端口134。为了简化的目的,仅示出四个下游端口134,但应当理解的是,USB定时集线器130可具有更多或更少的下游端口。USB定时集线器130还具有用于在USB定时集线器130和外部时序装置之间传递时序信息的外部时序端口。这种外部时序装置可为同步的仪器系统,例如PXI、PXI-express、以太网、LXI或VXI系统或能够提供或使用时序信息的任意其它系统。

USB定时集线器130具有超高速集线器功能元件138、非超高速集线器功能元件140、USB装置142、同步器144以及多个多路复用器146。可选择地,超高速集线器功能元件138和非超高速集线器功能元件140可被结合于复合装置中。

USB装置142可为超高速或非超高速装置,且被连接至超高速数据总线148和非超高速数据总线150。超高速集线器功能元件138和非超高速集线器功能元件140的每个下游连接分别(包括USB装置142所连接的)为并行连接,且为清楚起见,在图4A中仅被表示为总线。

USB装置142可用于通过通信信道152控制同步器144的某些参数,依次在上游USB主机控制器和前述连接至外部时序端口136的外部时序装置之间经由将同步器144和外部时序端口136耦合的外部时序信道154传递时序信息。各个多路复用器146被分配给每个外部下游USB端口134,由USB装置142经控制总线156来控制,以将非超高速通信150从非超高速USB集线器140传递至每个下游端口134,或者相反地(经通路时序信息和信号总线158)将时序信息和信号从同步器144传递到每个下游端口134。时序信息和信号总线158为每个多路复用器146提供专用的并行连接,并在其它时序信息中包含时钟、触发、循环时间测量信号和时间概念(notion of time)。

超高速集线器功能元件138和非超高速集线器功能元件140分别通过具有各自第一和第二检测点164、166的第一和第二上游信道160、162而被耦合到上游端口132。同步器144经第一和第二信道168、170分别在检测点164、166处观测超高速USB数据通信流和非超高速USB数据通信流,从而同步器144可使同步器144的本地时钟(未示出)与USB主机控制器的时间概念同步。可选择地,同步器144可仅(经第二信道170)观测非超高速USB数据通信流,如果USB装置142为非超高速装置,则这种情况一定存在。

此外,同步器144能够基于级联同步方式通过对其本地时钟和绝对时间寄存器的相位进行调节而调节其时间概念,该绝对时间寄存器位于USB网络树中又一超高速或非超高速USB定时集线器的下方。

在该实施方式的变化中,同步器144被配置为在第二检测点166处检测非超高速数据流,并经适当配置的多路复用器146(如图5B所示被配置)而将直接的副本下游(direct copy downstream)传递至下游USB装置。这允许USB装置通过超高速通信信道进行通信,然而仍接收位于非超高速同步信道上的周期性数据结构。此外,来自这种附接的USB装置的上游信号将需要通过同步器144按规定路线传送,并通过第二检测点166(可能通过可选择的多路复用器-未示出-位于第二检测点166处)被传送回上游信号通路中。

图4B为根据本发明另一个实施方式的同步USB装置190的示意图。同步USB装置190具有超高速USB功能元件192、非超高速USB功能元件194、同步器196以及多路复用器198。

同步USB装置190经连接器200被连接到USB(未示出)。超高速USB功能元件192经第一信道202从连接器200接收超高速数据信号,并且沿第二信道204(包括USB D+/D-信令线路)、经多路复用器198到非超高速USB功能元件194的路线从连接器200接收非超高速数据信号。多路复用器198也可截取第二信道202上的非超高速USB信号,并将它们经第三信道206传送至同步器196,从而使USB装置190成为同步USB装置。可替代地,多路复用器198可将第二信道204上的非超高速USB数据信号复制到第三信道206上,从而允许第二信道204上的非超高速USB数据信号被非超高速USB功能元件194和同步器196同时接收。

为了更加清楚地描述图4A的USB定时集线器130的操作,在图5A中以210以及在图5B中以210′示出USB定时集线器130的简化实施例。为简化起见,这些附图仅图示出一个代表性的下游端口134(虽然在实践中通常会提供多个下游端口),并且相同的附图标记已经用于图4A中。在这些实施例中,将USB装置142图示为非超高速USB装置,因此被内部连接到非超高速USB集线器功能元件140的下游端口135。如果需要,USB装置142可替换地连接至超高速集线器功能元件138。然而,期望将USB装置142连接至非超高速USB集线器功能元件140,从而使非超高速通信信道(和因此同步信道)保持到USB集线器130。

参照图5A,在下游端口134的正常运行中,USB装置142控制多路复用器146的状态,如该图所图示,多路复用器146被配置为将非超高速USB数据信号从非超高速USB集线器功能元件140传递至下游端口134。在正常条件下,超高速和非超高速信号被提供到下游端口134,以允许超高速或非超高速装置到下游的连接。

图5B为被配置成通过非超高速USB D+/D-USB的数据信令线路而提供超高速同步信道的USB定时集线器130的配置的示意图。通过被连接到并处于下游端口134的下游的超高速USB装置(未示出)请求提供主机控制器的这种同步信道,其依次请求USB装置142建立这种用于下游端口134的配置,从而建立了这种方案。然后,同步器144完全控制下游D+/D-数据信令线路到附接的上述超高速USB装置。然后,同步器144能够经多路复用器146传送和从下游端口143接收周期性时钟载波信号、专用时钟信号、电缆循环时间测量信号、触发信号、绝对时间基准信号、含有任意给定的绝对时间基准信号或需要使本地时钟或下游超高速USB装置的运行与来自主机控制器的时间概念或来自外部时序端口136(参见图4A)的外部时间概念同步的任意其它信号的绝对时间的数据的任意组合。

图6为根据本发明又一实施方式的混合的超高速和非超高速同步USB网络260的示意图。USB网络260包括主机控制器262、第一、第二、第三和第四USB定时集线器264a、264b、264c、264d、非超高速USB装置266以及多个超高速USB装置168。

USB网络260的混合装置的特性意味着非超高速USB装置266通过非超高速同步信道270被同步,而超高速USB装置268通过超高速同步信道272被同步。由(USB定时集线器264a的)下游集线器端口274跨越的网络支路仅包含超高速USB装置268,因此在该支路中的所有同步信道都为超高速同步信道272。通过对比,由(USB定时集线器264a的)下游集线器端口276跨越的网络支路包含超高速和非超高速USB装置两者。因此下游集线器端口276提供非超高速同步信道,其在到所附接的超高速USB装置的(USB定时集线器264d的)端口278的又一下游处变为超高速同步信道。

由(USB定时集线器264a的)集线器端口274跨越的网络支路可包含非超高速同步信道,但在该支路中仅存在超高速USB装置允许超高速同步信道被使用。

应当注意的是,在USB网络260中术语“最上方USB集线器”(如此处所使用的)是位于树形网络的顶部的USB集线器,即在主机控制器262中的USB集线器(未示出)。

图7为根据本发明实施方式的图示同步的超高速和非超高速USB装置对的时序信号的示意性时序图300。

非超高速帧起始包302被用作具有非超高速USB装置的标称时钟相位304的非超高速(或“HS”)装置的同步基准。需要注意的是,时钟脉冲304的上升边与帧起始包302同相。

同样地,在ITP窗口308内的任何地方可被传递到超高速USB装置的超高速等时时间戳包(ITP)306,提供用于同步基准的时间戳;该时间戳与帧起始包302同步。超高速(或“SS”)USB装置具有标称时钟相位310。

然而,由于在SOF和ITP包之间的传播时间差,在时钟信号的相位中存在不确定性。在标称的意义上,它们两者的相位将与他们各自基准信号的接收时间对准。

非超高速USB装置信号传播时间通过主机控制器将HS ping 312消息发送到非超高速USB装置并测量HS ping 312的传输和(HS)响应信号314的接收之间的总时间延迟而确定。以316示出单向的传播时间;以318示出非超高速谐振时钟相对于SOF包的真实相位。

用于超高速USB装置,同样地,SS ping 320和各自的响应322指示以324示出的单向传播时间。然后,超高速谐振时钟的真实相位以326示出,其中以328示出在超高速和非超高速USB装置之间的相位差。知道了这两个时域和相对相位,允许超高速和非超高速USB装置的精确相位同步。

本领域技术人员易于进行在本发明的范围内的修改。因此应当理解的是,本发明不限于通过上文实施例所描述的具体实施方式,并且本文描述的各种实施方式的结合对于本领域技术人员是明显的。

在前述对本发明的描述以及所附权利要求中,除了由于表达语言或必要的暗示而上下文另有要求之外,词语“主机控制器”包含所有形式的USB主机控制器,包括标准的USB主机控制器、移动USB(USB-on-the-go)主机控制器以及无线USB主机控制器。

在前述对本发明的描述以及所附权利要求中,除了由于表达语言或必要的暗示而上下文另有要求之外,词“包括”或诸如“包含”或“含有”之类的变化形式以包括在内的意义被使用,也就是说,用于详列所述特征的存在,但不排除在本发明的各个实施方式中其他特征的存在或增加。

而且,此处对背景技术的任何引用并不旨在表示暗示这种背景技术形成或已形成任何国家的公知常识的一部分。

Claims (41)

1.一种使多个超高速USB装置和多个非超高速USB装置的运行同步的方法,包括:

为所述多个超高速USB装置的每一个建立超高速同步信道;

为所述多个非超高速USB装置的每一个建立非超高速同步信道;

使所述多个超高速USB装置的每一个的各个本地时钟同步;

使所述多个非超高速USB装置的每一个的各个本地时钟同步;和

使所述超高速同步信道和非超高速同步信道同步,从而所述超高速装置和非超高速装置能同步地运行。

2.根据权利要求1所述的方法,包括利用等时传送方法使所述超高速USB装置的每一个的所述本地时钟谐振或锁频,所述等时传送方法包括:

在所述主机控制器和所述各个超高速USB装置之间打开至少一个等时通信管道;

保证所述各个超高速USB装置处于链路状态U0,以准备接收等时时间戳包(ITP);

所述主机控制器将多个多播传送周期性等时时间戳包发送到所述等时端点的每一个;

将所述各个超高速USB装置的各个本地时钟锁定为来自所述周期性等时时间戳包(ITP)的信息;

从而将所述周期性等时时间戳包内包含的时间戳用作基准时间,来使所述各个超高速USB装置的各个本地时钟与所述主机控制器的时域谐振,并且利用所述等时时间戳包从所述主机控制器到所述各个超高速USB装置的传播时间,来使所述各个本地时钟同步或相位对准。

3.根据权利要求2所述的方法,进一步包括:

确定和补偿所述各个超高速USB装置的所述各个本地时钟由于所述等时时间戳包从所述主机控制器或USB集线器到所述各个超高速USB装置的相对传播时间所引起的相位误差。

4.根据权利要求1所述的方法,包括另外利用不用的非超高速信号导线使所述超高速USB装置的每一个的各个本地时钟谐振或锁频,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述超高速USB装置的上游端口处,多路分离来自D+/D-信令线路的同步信息;和

将所述各个超高速USB装置的所述各个本地时钟锁定到所述同步信息。

5.根据权利要求4所述的方法,其中所述同步信息包括触发信号、时钟信号和时钟相位信息。

6.根据权利要求4所述的方法,进一步包括:

确定和补偿所述各个超高速USB装置的各个本地时钟由于所述同步信息从所述主机控制器或USB集线器到所述各个超高速USB装置的每一个的相对传播时间所引起的相位误差。

7.根据权利要求1所述的方法,其中,使所述非超高速USB装置的各个本地时钟同步包括:

监控在所述各个非超高速USB装置本地的USB数据通信流;

对来自所述USB数据流的多个周期性信号结构解码;

将所述非超高速USB装置的所述各个本地时钟锁定到来自所述周期性信号结构的信息;

从而将所述周期性信号结构用作基准时间,来使所述非超高速USB装置的所述各个本地时钟与所述主机控制器的时域谐振,并且利用所述周期性信号结构从所述主机控制器到所述各个非超高速USB装置的各个传播时间,来使所述本地时钟同步或相位对准。

8.根据权利要求7所述的方法,进一步包括:

确定和补偿所述非超高速USB装置的所述各个本地时钟由于所述周期性信号结构从所述主机控制器或USB集线器到所述各个非超高速USB装置的各个相对传播时间所引起的相位误差。

9.根据权利要求7或8所述的方法,其中,所述周期性信号结构包括USB帧起始包。

10.根据权利要求1至9中任一项所述的方法,其中,使所述超高速同步信道和非超高速同步信道同步包括:

在所述非超高速同步信道的时域中,确定各个第一等时数据包和等时时间戳包从所述主机控制器到所述各个超高速USB装置的每一个的各自传输时间;

向所述主机控制器报告所述各自传输时间;和

所述主机控制器在所述超高速USB装置的各个时域和所述非超高速USB装置的时域之间创建映射;和

使所述超高速USB装置的各个USB装置功能电路的多个运行或事件的每一个的各个本地时间与所述主机控制器的时域匹配;

从而所述运行或事件的每一个能被反向映射到所述非超高速USB装置的时域。

11.一种使USB网络中多个超高速USB装置和非超高速USB装置的各个本地时钟同步的方法,该USB网络包括多个USB集线器、一个以上的超高速USB装置和一个以上的非超高速USB装置,该方法包括:

确定所述USB网络的连接布局;

在所述USB网络的最上方USB集线器处建立非超高速同步信道;

在所述USB网络的每个网络支路中识别在其各个子网络中不包含任何非超高速USB装置的各个最高USB集线器端口,每个各个最高USB集线器端口被设置于每个所述网络支路的对应的最高USB集线器中;

建立从所述各个最高USB集线器端口到每个所述超高速USB装置的各个超高速同步信道,每个所述超高速USB装置附接到所述各个最高USB集线器端口;

使所述各个最高USB集线器的各个本地时钟通过它们各自的上游非超高速同步信道同步;

使所述非超高速USB装置的所述本地时钟通过各自的非超高速同步信道同步;和

使所述各个超高速USB装置的所述本地时钟通过所述各自的超高速同步信道同步;

从而使所述超高速同步信道与在其各个网络支路中对应的各个所述最高USB集线器的时间概念同步,并且使所述最高USB集线器的各个本地时钟与非超高速同步信道同步。

12.根据权利要求11所述的方法,包括另外利用不用的非超高速信号导线使所述超高速USB装置的所述各个本地时钟的每一个谐振或锁频,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述超高速USB装置的上游端口处,多路分离来自D+和D-信令线路的同步信息;和

将所述各个超高速USB装置的所述各个本地时钟锁定到所述同步信息。

13.根据权利要求12所述的方法,进一步包括:

确定和补偿所述本地时钟由于所述同步信息从所述USB主机控制器或USB集线器到所述多个USB装置的每一个的相对传播时间所引起的相位误差。

14.根据权利要求11所述的方法,包括使所述非超高速USB装置的所述本地时钟同步包括:

监控在所述非超高速USB装置的每一个本地的USB数据通信流;

对来自所述USB数据流的多个周期性信号结构解码;

将所述非超高速USB装置的所述各个本地时钟锁定到来自所述周期性信号结构的信息;

从而将所述周期性信号结构(优选为USB帧起始包)用作基准时间,来使所述非超高速USB装置的所述各个本地时钟与所述主机控制器的时域谐振,并且利用所述周期性信号结构自所述主机控制器的相对传播时间而使所述非超高速USB装置的所述本地时钟同步或相位对准。

15.根据权利要求14所述的方法,其中,所述周期性信号结构包括USB帧起始包。

16.根据权利要求14所述的方法,进一步包括:

确定和补偿所述非超高速USB装置的所述本地时钟由于所述周期性信号结构从所述USB主机控制器或USB集线器到所述各个非超高速USB装置的相对传播时间所引起的相位误差。

17.根据权利要求11所述的方法,进一步包括:

使所述USB集线器和所述非超高速USB装置的所述各个本地时钟锁定到或同步于基本相同的频率;

测量非超高速信号从所述最上方USB集线器到所述最高USB集线器和非超高速USB装置的每一个的各个往返传播时间;

确定非超高速信号到所述USB集线器和非超高速USB装置的每一个的各个下游传播时间或相对下游传播时间;

同步或调节所述USB集线器的所述本地时钟的每一个的相位和包含在所述非超高速同步信道中的所述非超高速USB装置的所述本地时钟的每一个的相位;和

为所述USB装置的每一个提供公共的时间概念。

18.根据权利要求17所述的方法,包括另外利用不用的非超高速信号导线使所述超高速USB装置的所述各个本地时钟谐振于或锁频到所述最高USB集线器,包括:

在上游USB主机控制器或USB集线器处,将附加的同步信息多路复用到高速USB D+和D-数据信令线路上;

在所述各个超高速USB装置的上游端口处,多路分离来自D+/D-信令线路的同步信息;

将所述超高速USB装置的所述各个本地时钟锁定到所述同步信息,

其中,所述附加的同步信息由所述最上方USB集线器的所述本地时钟产生,从而使所述超高速USB装置的所述各个本地时钟与所述非超高速同步信道的时间概念同步。

19.根据权利要求18所述的方法,进一步包括:

确定和补偿所述超高速USB装置的所述本地时钟由于所述附加的同步信息从所述各个最高USB集线器到所述各个超高速USB装置的相对传播时间所引起的相位误差。

20.一种用于使USB网络中一个以上的超高速USB装置和一个以上的非超高速USB装置同步的设备,包括:

具有超高速USB上游端口的USB集线器;

多个超高速USB下游端口;

适于执行USB 3.0集线器功能的USB集线器功能电路,该功能提供到所述上游端口和到所述多个下游端口的连接;和

至少一个USB装置功能电路,所述USB装置功能电路被连接至所述下游端口中的一个;

解码电路,用于在所述上游端口处对来自非超高速USB数据流的周期性信号结构解码;

谐振器电路,适于使所述设备的本地时钟与所述周期性信号结构谐振;

适于使所述本地时钟与外部的时间概念同步的同步器;

适于产生所述本地时钟所参考的附加的同步信息的电路;和

能操作以选择性地使所述设备的每个下游USB端口的下游非超高速D+/D-数据信令线路从它们各个USB集线器功能元件下游端口失效的电路;

多路复用器,用于在所述多个下游USB连接器的每一个处将来自所述本地时钟的所述附加的同步信息多路复用到所述下游D+/D-信令线路上,能操作以将所述非超高速USB D+/D-信号引导向具有附接的非超高速装置的任意下游USB连接器,并将所述附加的同步信息引导向具有附接的超高速USB装置的任意所述下游USB连接器;和

定时器,适于确定信号从所述设备到一个以上附接的下游USB装置的各个往返时间间隔;

其中,所述USB装置功能电路适于将由定时器确定的所述往返时间间隔传输到所述USB网络的USB主机控制器。

21.根据权利要求20所述的设备,其中,所述USB装置功能电路适于执行非超高速装置功能。

22.根据权利要求20所述的设备,其中,所述USB装置功能电路适于执行超高速装置功能。

23.根据权利要求20至22中任一项所述的设备,其中,所述外部时间概念由所述USB主机控制器提供。

24.根据权利要求20至23中任一项所述的设备,其中,所述同步器还适于使所述本地时钟与外部接口谐振。

25.根据权利要求24所述的设备,适于从所述外部接口接收所述外部时间概念。

26.根据权利要求24或25所述的设备,其中,所述外部接口包括GPS时钟、PXI机箱槽1时序控制器、以太网接口、IEEE-1588精确时间协议以太网、网络时间协议以太网、原子钟或靶场间仪器组(IRIG)接口中的任意一个或多个。

27.根据权利要求20至26中任一项所述的设备,进一步包括:

USB主机控制器功能元件,适于连接到所述USB集线器的所述上游端口。

28.根据权利要求20至27中任一项所述的设备,其中,所述谐振器电路包括:

用于观测在任意附接的USB装置的各个连接点或下游端口本地的USB数据流的电路;

用于对来自所述USB数据流的周期性信号结构解码的电路;

用于对应对来自所述USB数据流的周期性数据结构解码而在所述设备本地产生事件信号的电路;

用于相对于所述事件信号的频率锁定所述本地时钟的频率的电路。

29.一种用于向一个以上超高速连接的USB装置提供同步信号的设备,该设备包括:

包含超高速USB上游端口的USB集线器;和

多个超高速USB下游端口;

时钟或时钟电路;

适于产生所述本地时钟所参考的同步信息的电路;

能操作以将所述同步信息多路复用到选定的一个以上所述下游端口的D+/D-信令线路上,USB装置以超高速USB模式被附接和连接到选定的一个以上所述下游端口。

30.一种使以超高速模式连接的USB装置的时钟与附接到该USB装置的USB集线器的时钟同步的方法,该方法包括:

从所述USB集线器的所述时钟产生同步信息;

将所述同步信息多路复用到所述USB装置所附接到的所述USB集线器的下游端口的不用的D+/D-信令线路上;

使所述USB装置的所述时钟与所述同步信息同步;

从而使所述USB装置连接到主机控制器并通过所述USB集线器利用超高速USB协议与主机控制器通信,并且同时与所述USB集线器的所述时钟的时间概念同步。

31.根据权利要求30所述的方法,其中,所述同步信息包括所述USB集线器的所述时钟能与其谐振的谐振信息。

32.根据权利要求30或31所述的方法,其中,所述谐振信息包括周期性信号。

33.根据权利要求30至32中任一项所述的方法,其中,所述同步信息包含所述USB集线器的所述时钟的时间概念。

34.根据权利要求30至33中任一项所述的方法,其中,所述同步信息包括一个以上的触发信号。

35.根据权利要求30至34中任一项所述的方法,进一步包括确定从所述USB集线器到所述USB装置的信号传播时间。

36.根据权利要求35所述的方法,其中,根据所述信号传播时间的确定而对所述USB装置的所述时钟的相位进行调节。

37.一种使公共USB网络的超高速USB装置和非超高速USB装置的相位同步的方法,包括:

使所述非超高速USB装置的本地时钟相对于周期性帧起始包谐振;

使所述超高速USB装置的本地时钟相对于周期性等时时间戳包谐振;

确定在基本接近所述USB网络的顶部的点和所述非超高速USB装置之间的非超高速传播时间;

确定在基本接近所述USB网络的顶部的点和所述超高速USB装置之间以及返回的超高速传播时间;

确定所述超高速传播时间和所述非超高速传播时间之间的差;和

根据所述超高速传播时间和所述非超高速传播时间之间的所述差调节所述本地时钟的相位。

38.根据权利要求37所述的方法,其中,所述非超高速传播时间被确定为单向或往返传播时间。

39.根据权利要求37或38所述的方法,其中,所述超高速传播时间被确定为单向或往返传播时间。

40.根据权利要求37至39中任一项所述的方法,进一步包括:

使又一非超高速USB装置的本地时钟相对于周期性帧起始包谐振;

确定在基本接近所述USB网络的顶部的点和所述又一非超高速USB装置之间的又一非超高速传播时间;

确定所述超高速传播时间和所述又一非超高速传播时间之间的差;和

根据所述超高速传播时间和又一非超高速传播时间之间的所述差调节所述非超高速USB装置的所述本地时钟的相位。

41.根据权利要求37至40中任一项所述的方法,进一步包括:

使又一超高速USB装置的本地时钟相对于周期性帧起始包谐振;

确定在基本接近所述USB网络的顶部的点和所述又一超高速USB装置之间的又一超高速传播时间;

确定所述又一超高速传播时间和所述非超高速传播时间之间的差;和

根据所述又一超高速传播时间和所述非超高速传播时间之间的所述差调节所述非超高速USB装置的所述本地时钟的相位。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US17990409P | 2009-05-20 | 2009-05-20 | |

| US61/179,904 | 2009-05-20 | ||

| PCT/AU2010/000605 WO2010132944A1 (en) | 2009-05-20 | 2010-05-20 | Synchronous network of superspeed and non-superspeed usb devices |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN102439532A true CN102439532A (zh) | 2012-05-02 |

Family

ID=43125664

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2010800219269A Pending CN102439531A (zh) | 2009-05-20 | 2010-05-20 | 高密度、低抖动、同步usb扩展 |

| CN2010800218675A Pending CN102428423A (zh) | 2009-05-20 | 2010-05-20 | 用于分布式同步时钟架构的抖动减少方法和设备 |

| CN2010800219729A Pending CN102439532A (zh) | 2009-05-20 | 2010-05-20 | 超高速和非超高速usb装置的同步网络 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2010800219269A Pending CN102439531A (zh) | 2009-05-20 | 2010-05-20 | 高密度、低抖动、同步usb扩展 |

| CN2010800218675A Pending CN102428423A (zh) | 2009-05-20 | 2010-05-20 | 用于分布式同步时钟架构的抖动减少方法和设备 |

Country Status (7)

| Country | Link |

|---|---|

| US (11) | US20120066417A1 (zh) |

| EP (10) | EP2433196B1 (zh) |

| JP (4) | JP5575229B2 (zh) |

| CN (3) | CN102439531A (zh) |

| AU (7) | AU2010251767A1 (zh) |

| CA (3) | CA2761363A1 (zh) |

| WO (10) | WO2010132942A1 (zh) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103309397A (zh) * | 2013-06-17 | 2013-09-18 | 杭州锐达数字技术有限公司 | 基于usb的数据采集设备的同步采样方法 |

Families Citing this family (93)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE1150596B (de) * | 1960-01-15 | 1963-06-20 | Wilmot Breeden Ltd | Verschluss fuer Fahrzeugtueren |

| US20120066417A1 (en) * | 2009-05-20 | 2012-03-15 | Chronologic Pty. Ltd. | Synchronisation and trigger distribution across instrumentation networks |

| US8135883B2 (en) * | 2010-01-19 | 2012-03-13 | Standard Microsystems Corporation | USB hub apparatus supporting multiple high speed devices and a single super speed device |

| US8428045B2 (en) * | 2010-03-16 | 2013-04-23 | Harman International Industries, Incorporated | Media clock recovery |

| US8645601B2 (en) * | 2010-06-11 | 2014-02-04 | Smsc Holdings S.A.R.L. | Methods and systems for performing serial data communication between a host device and a connected device |

| US8484387B2 (en) * | 2010-06-30 | 2013-07-09 | Silicon Image, Inc. | Detection of cable connections for electronic devices |

| US8719475B2 (en) * | 2010-07-13 | 2014-05-06 | Broadcom Corporation | Method and system for utilizing low power superspeed inter-chip (LP-SSIC) communications |

| US8560754B2 (en) * | 2010-09-17 | 2013-10-15 | Lsi Corporation | Fully integrated, low area universal serial bus device transceiver |

| EP2434360B1 (de) * | 2010-09-22 | 2020-01-08 | Siemens Aktiengesellschaft | Bewegungssteuerungssystem |

| US8364870B2 (en) * | 2010-09-30 | 2013-01-29 | Cypress Semiconductor Corporation | USB port connected to multiple USB compliant devices |

| JP5269047B2 (ja) * | 2010-11-29 | 2013-08-21 | シャープ株式会社 | 電子機器システム、電子機器及び接続機器 |

| US8825925B1 (en) * | 2011-02-14 | 2014-09-02 | Cypress Semiconductor Corporation | Systems and methods for super speed packet transfer |

| CN102221860B (zh) * | 2011-06-14 | 2012-09-12 | 浙江红苹果电子有限公司 | 一种机箱间背板信号无限级联的方法及其装置 |

| TWI539289B (zh) * | 2011-06-16 | 2016-06-21 | Eever Technology Inc | 低耗電的usb3.0主控制裝置及降低usb3.0主控制裝置耗電的方法 |

| US8799532B2 (en) | 2011-07-07 | 2014-08-05 | Smsc Holdings S.A.R.L. | High speed USB hub with full speed to high speed transaction translator |

| US8996747B2 (en) | 2011-09-29 | 2015-03-31 | Cypress Semiconductor Corporation | Methods and physical computer-readable storage media for initiating re-enumeration of USB 3.0 compatible devices |

| CN102955585A (zh) * | 2011-08-24 | 2013-03-06 | 鸿富锦精密工业(深圳)有限公司 | 鼠标 |

| US8843664B2 (en) | 2011-09-29 | 2014-09-23 | Cypress Semiconductor Corporation | Re-enumeration of USB 3.0 compatible devices |

| JP2013090006A (ja) * | 2011-10-13 | 2013-05-13 | Nikon Corp | 電子機器およびプログラム |

| US8898354B2 (en) * | 2011-12-15 | 2014-11-25 | Icron Technologies Corporation | Methods and devices for synchronizing to a remotely generated time base |

| US9590411B2 (en) | 2011-12-15 | 2017-03-07 | Schweitzer Engineering Laboratories, Inc. | Systems and methods for time synchronization of IEDs via radio link |

| US9697159B2 (en) * | 2011-12-27 | 2017-07-04 | Intel Corporation | Multi-protocol I/O interconnect time synchronization |

| JP5763519B2 (ja) * | 2011-12-28 | 2015-08-12 | ルネサスエレクトロニクス株式会社 | Usbハブコントローラ、usbホストコントローラ、およびシステム |

| TWI482026B (zh) * | 2012-02-07 | 2015-04-21 | Etron Technology Inc | 低耗電的usb3.0主控制裝置與降低usb3.0主控制裝置耗電的方法 |

| US20130254440A1 (en) * | 2012-03-20 | 2013-09-26 | Icron Technologies Corporation | Devices and methods for transmitting usb termination signals over extension media |

| EP2845111A4 (en) | 2012-05-02 | 2015-12-23 | Intel Corp | CONFIGURATION OF A REMOTE-M-PHY |

| JP5970958B2 (ja) * | 2012-05-22 | 2016-08-17 | 富士通株式会社 | 情報処理装置、遅延差測定方法、及び遅延差測定プログラム |

| AU2013204757A1 (en) * | 2012-06-03 | 2013-12-19 | Chronologic Pty Ltd | Synchronisation of a system of distributed computers |

| US9087158B2 (en) | 2012-06-30 | 2015-07-21 | Intel Corporation | Explicit control message signaling |

| US20140019777A1 (en) * | 2012-07-11 | 2014-01-16 | Tsun-Te Shih | Power data communication architecture |

| CN103577365A (zh) * | 2012-07-19 | 2014-02-12 | 财团法人工业技术研究院 | 便携式电子装置 |

| US9709680B2 (en) | 2012-09-08 | 2017-07-18 | Schweitzer Engineering Laboratories, Inc. | Quality of precision time sources |

| ES2552829B1 (es) | 2012-10-19 | 2017-03-23 | Schweitzer Engineering Laboratories, Inc. | Conmutador de distribución de tiempo |

| US9400330B2 (en) | 2012-10-19 | 2016-07-26 | Schweitzer Engineering Laboratories, Inc. | Manipulation resilient time distribution network |

| US9599719B2 (en) | 2012-10-19 | 2017-03-21 | Schweitzer Engineering Laboratories, Inc. | Detection of manipulated satellite time signals |

| CA2886762A1 (en) | 2012-10-19 | 2014-04-24 | Schweitzer Engineering Laboratories, Inc. | Time distribution device with multi-band antenna |

| KR20140065074A (ko) * | 2012-11-21 | 2014-05-29 | 삼성전자주식회사 | 모바일 디바이스 및 유에스비 허브 |

| TWI497306B (zh) * | 2012-11-29 | 2015-08-21 | Faraday Tech Corp | 超高速通用序列匯流排集線器及其相關流量管理方法 |

| US9759816B2 (en) | 2013-01-11 | 2017-09-12 | Schweitzer Engineering Laboratories, Inc. | Multi-constellation GNSS integrity check for detection of time signal manipulation |

| US9709682B2 (en) | 2013-05-06 | 2017-07-18 | Schweitzer Engineering Laboratories, Inc. | Multi-constellation GNSS integrity check for detection of time signal manipulation |

| WO2014116226A1 (en) * | 2013-01-25 | 2014-07-31 | Hewlett Packard Development Company, L.P. | Usb controllers coupled to usb ports |

| KR20140106184A (ko) * | 2013-02-26 | 2014-09-03 | 삼성전자주식회사 | 케이블, 이와 연결되는 이동 단말 및 그 동작 방법 |

| US20140244852A1 (en) * | 2013-02-27 | 2014-08-28 | Ralink Technology Corp. | Method of Reducing Mutual Interference between Universal Serial Bus (USB) data transmission and wireless data transmission |

| WO2014137311A1 (en) * | 2013-03-04 | 2014-09-12 | Empire Technology Development Llc | Virtual instrument playing scheme |

| JP2014217039A (ja) * | 2013-04-30 | 2014-11-17 | 富士通株式会社 | 伝送装置および同期制御方法 |

| US9083503B2 (en) | 2013-05-02 | 2015-07-14 | Schweitzer Engineering Laboratories, Inc. | Synchronized clock event report |

| US9319100B2 (en) | 2013-08-12 | 2016-04-19 | Schweitzer Engineering Laboratories, Inc. | Delay compensation for variable cable length |

| CN104426025B (zh) * | 2013-09-03 | 2018-04-17 | 鸿富锦精密工业(深圳)有限公司 | 电子装置连接系统 |

| US11025345B2 (en) | 2013-09-19 | 2021-06-01 | Radius Universal Llc | Hybrid cable providing data transmission through fiber optic cable and low voltage power over copper wire |

| US10855381B2 (en) * | 2013-09-19 | 2020-12-01 | Radius Universal Llc | Fiber optic communications and power network |

| US10277330B2 (en) | 2013-09-19 | 2019-04-30 | Radius Universal Llc | Fiber optic communications and power network |

| US9133019B2 (en) * | 2013-12-03 | 2015-09-15 | Barry John McCleland | Sensor probe and related systems and methods |

| CN104750649B (zh) * | 2013-12-31 | 2017-09-29 | 中核控制系统工程有限公司 | 开放性拓扑结构总线的同步时序控制方法 |

| US9606955B2 (en) | 2014-02-10 | 2017-03-28 | Intel Corporation | Embedded universal serial bus solutions |

| US9270442B2 (en) | 2014-04-29 | 2016-02-23 | Schweitzer Engineering Laboratories, Inc. | Time signal propagation delay correction |

| US9811488B2 (en) | 2014-04-29 | 2017-11-07 | Mcci Corporation | Apparatus and methods for dynamic role switching among USB hosts and devices |

| US10165031B2 (en) * | 2014-05-04 | 2018-12-25 | Valens Semiconductor Ltd. | Methods and systems for incremental calculation of latency variation |

| US9425652B2 (en) | 2014-06-16 | 2016-08-23 | Schweitzer Engineering Laboratories, Inc. | Adaptive holdover timing error estimation and correction |

| CN104133801A (zh) * | 2014-06-18 | 2014-11-05 | 长芯盛(武汉)科技有限公司 | 数据传输装置及方法 |

| TWI509418B (zh) * | 2014-06-30 | 2015-11-21 | Chant Sincere Co Ltd | 資料轉換系統與及其控制方法 |

| CN104156036A (zh) * | 2014-07-08 | 2014-11-19 | 北京中科泛华测控技术有限公司 | 多板卡同步互连方法和主板卡、从板卡 |

| JP6458388B2 (ja) * | 2014-07-30 | 2019-01-30 | ブラザー工業株式会社 | 読取装置、その制御方法およびコンピュータプログラム |

| US10579574B2 (en) | 2014-09-30 | 2020-03-03 | Keysight Technologies, Inc. | Instrumentation chassis with high speed bridge board |

| US9813173B2 (en) | 2014-10-06 | 2017-11-07 | Schweitzer Engineering Laboratories, Inc. | Time signal verification and distribution |

| US9710406B2 (en) * | 2014-12-15 | 2017-07-18 | Intel Corporation | Data transmission using PCIe protocol via USB port |

| KR101585063B1 (ko) | 2014-12-22 | 2016-01-13 | 포항공과대학교 산학협력단 | 외부 클락신호를 사용하지 않는 직렬 데이터 통신용 디바이스 phy |

| US20160344661A1 (en) * | 2015-05-18 | 2016-11-24 | Justin T. Esgar | System and method for linking external computers to a server |

| CN105550134B (zh) * | 2015-12-07 | 2018-04-03 | 上海兆芯集成电路有限公司 | 高速数据接口主机端控制器 |

| CN105512071B (zh) * | 2015-12-07 | 2018-04-03 | 上海兆芯集成电路有限公司 | 高速数据接口主机端控制器 |

| CN106909198B (zh) * | 2015-12-22 | 2020-11-06 | 华硕电脑股份有限公司 | 一种外接装置、电子装置及电子系统 |

| US10375108B2 (en) | 2015-12-30 | 2019-08-06 | Schweitzer Engineering Laboratories, Inc. | Time signal manipulation and spoofing detection based on a latency of a communication system |

| JP2017163204A (ja) * | 2016-03-07 | 2017-09-14 | APRESIA Systems株式会社 | 通信装置 |

| US10095653B2 (en) * | 2016-04-02 | 2018-10-09 | Intel Corporation | Apparatuses, systems, and methods for accurately measuring packet propagation delays through USB retimers |

| US10503684B2 (en) * | 2016-07-01 | 2019-12-10 | Intel Corporation | Multiple uplink port devices |

| US10527732B2 (en) | 2017-02-09 | 2020-01-07 | Schweitzer Engineering Laboratories, Inc. | Verification of time sources |

| JP6897307B2 (ja) * | 2017-05-19 | 2021-06-30 | セイコーエプソン株式会社 | 回路装置、電子機器、ケーブルハーネス及びデータ転送方法 |

| US20180376034A1 (en) * | 2017-06-22 | 2018-12-27 | Christie Digital Systems Usa, Inc. | Atomic clock based synchronization for image devices |

| US20190025872A1 (en) * | 2017-07-18 | 2019-01-24 | Qualcomm Incorporated | Usb device with clock domain correlation |

| CN111149077A (zh) * | 2018-01-25 | 2020-05-12 | 英特尔公司 | 分立式通信端口组件的电源管理 |

| US10896106B2 (en) * | 2018-05-10 | 2021-01-19 | Teradyne, Inc. | Bus synchronization system that aggregates status |

| EP3791279A4 (en) * | 2018-05-11 | 2022-01-26 | Cigent Technology, Inc. | METHOD AND SYSTEM FOR ENHANCED DATA CONTROL AND DATA ACCESS |

| US11630424B2 (en) | 2018-07-13 | 2023-04-18 | Schweitzer Engineering Laboratories, Inc. | Time signal manipulation detection using remotely managed time |

| US10713185B2 (en) * | 2018-07-16 | 2020-07-14 | Logitech Europe S.A. | Wireless communication with peripheral device |

| US10819727B2 (en) | 2018-10-15 | 2020-10-27 | Schweitzer Engineering Laboratories, Inc. | Detecting and deterring network attacks |

| CN109855798A (zh) * | 2018-12-09 | 2019-06-07 | 北京航天计量测试技术研究所 | 一种基于pxi总线技术的便携式压力在线检定装置 |

| US10912104B2 (en) | 2019-02-01 | 2021-02-02 | Schweitzer Engineering Laboratories, Inc. | Interleaved, static time division multiple access (TDMA) for minimizing power usage in delay-sensitive applications |

| CN110018977A (zh) * | 2019-03-20 | 2019-07-16 | 芯启源(上海)半导体科技有限公司 | 基于usb协议的侵权识别方法、系统、终端、及介质 |

| US10873402B2 (en) | 2019-04-30 | 2020-12-22 | Corning Research & Development Corporation | Methods and active optical cable assemblies for providing a reset signal at a peripheral end |

| US10884973B2 (en) | 2019-05-31 | 2021-01-05 | Microsoft Technology Licensing, Llc | Synchronization of audio across multiple devices |

| US11075534B2 (en) * | 2019-10-12 | 2021-07-27 | Hynetek Semiconductor Co., Ltd. | USB type-C interface circuit and charging method thereof, USB device |

| US11126220B2 (en) * | 2020-01-29 | 2021-09-21 | Dell Products L.P. | System and method for time synchronization between information handling systems |

| US11170800B2 (en) | 2020-02-27 | 2021-11-09 | Microsoft Technology Licensing, Llc | Adjusting user experience for multiuser sessions based on vocal-characteristic models |

| US20220327088A1 (en) * | 2021-04-12 | 2022-10-13 | Icron Technologies Corporation | Predicting free buffer space in a usb extension environment |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6092210A (en) * | 1998-10-14 | 2000-07-18 | Cypress Semiconductor Corp. | Device and method for synchronizing the clocks of interconnected universal serial buses |

| CN101281512A (zh) * | 2002-07-17 | 2008-10-08 | 菲博比特有限公司 | 同步多信道通用串行总线 |

| CN101401055A (zh) * | 2006-02-15 | 2009-04-01 | 菲博比特有限公司 | 分布式同步和定时系统 |

Family Cites Families (131)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4757460A (en) * | 1985-06-14 | 1988-07-12 | Zenith Electronics Corporation | Communications network with individualized access delays |

| GB2242800B (en) * | 1990-04-03 | 1993-11-24 | Sony Corp | Digital phase detector arrangements |

| JPH05161181A (ja) * | 1991-12-10 | 1993-06-25 | Nec Corp | 時刻同期方式 |

| US5553302A (en) * | 1993-12-30 | 1996-09-03 | Unisys Corporation | Serial I/O channel having independent and asynchronous facilities with sequence recognition, frame recognition, and frame receiving mechanism for receiving control and user defined data |

| US5832310A (en) * | 1993-12-30 | 1998-11-03 | Unisys Corporation | Serial I/O channel having dependent and synchronous sources of control data and user defined data |

| EP0683577A3 (de) * | 1994-05-20 | 1998-09-09 | Siemens Aktiengesellschaft | Weiterleitung von hochbitratigen Datenströmen über Datenausgänge eines Bausteins mit einer niedrigen internen Datenverarbeitungsrate |

| US5566180A (en) | 1994-12-21 | 1996-10-15 | Hewlett-Packard Company | Method for recognizing events and synchronizing clocks |

| US6219628B1 (en) * | 1997-08-18 | 2001-04-17 | National Instruments Corporation | System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations |

| JP3189774B2 (ja) * | 1998-01-28 | 2001-07-16 | 日本電気株式会社 | ビット同期回路 |

| FI106285B (fi) * | 1998-02-17 | 2000-12-29 | Nokia Networks Oy | Mittausraportointi tietoliikennejärjestelmässä |

| US6064679A (en) | 1998-05-01 | 2000-05-16 | Emulex Corporation | Hub port without jitter transfer |

| US6278710B1 (en) | 1998-09-10 | 2001-08-21 | Agilent Technologies, Inc. | Enhancements to time synchronization in distributed systems |

| US6665316B1 (en) | 1998-09-29 | 2003-12-16 | Agilent Technologies, Inc. | Organization of time synchronization in a distributed system |

| US8073985B1 (en) * | 2004-02-12 | 2011-12-06 | Super Talent Electronics, Inc. | Backward compatible extended USB plug and receptacle with dual personality |

| US6636912B2 (en) * | 1999-10-07 | 2003-10-21 | Intel Corporation | Method and apparatus for mode selection in a computer system |

| US6496895B1 (en) * | 1999-11-01 | 2002-12-17 | Intel Corporation | Method and apparatus for intializing a hub interface |

| JP3479248B2 (ja) * | 1999-12-17 | 2003-12-15 | 日本電気株式会社 | Atm伝送試験装置 |

| JP2001177570A (ja) * | 1999-12-17 | 2001-06-29 | Mitsubishi Electric Corp | 通信ネットワークシステム、通信ネットワークシステムにおけるスレーブ装置、マスタ装置および中継装置ならびに通信ネットワークシステムにおける同期制御方法 |

| US6407641B1 (en) * | 2000-02-23 | 2002-06-18 | Cypress Semiconductor Corp. | Auto-locking oscillator for data communications |

| US6297705B1 (en) * | 2000-02-23 | 2001-10-02 | Cypress Semiconductor Corp. | Circuit for locking an oscillator to a data stream |

| US6946920B1 (en) * | 2000-02-23 | 2005-09-20 | Cypress Semiconductor Corp. | Circuit for locking an oscillator to a data stream |

| JP3536792B2 (ja) * | 2000-02-28 | 2004-06-14 | ヤマハ株式会社 | 同期制御装置および同期制御方法 |

| US7080160B2 (en) * | 2000-04-27 | 2006-07-18 | Qosmetrics, Inc. | Method for creating accurate time-stamped frames sent between computers via a network |

| AU2001259867A1 (en) * | 2000-05-18 | 2001-11-26 | Brix Networks, Inc. | Hardware time stamping and registration of packetized data method and system |

| US6680970B1 (en) * | 2000-05-23 | 2004-01-20 | Hewlett-Packard Development Company, L.P. | Statistical methods and systems for data rate detection for multi-speed embedded clock serial receivers |

| JP2002007307A (ja) * | 2000-06-23 | 2002-01-11 | Fuji Photo Film Co Ltd | 機器制御装置及び方法 |

| US6343364B1 (en) | 2000-07-13 | 2002-01-29 | Schlumberger Malco Inc. | Method and device for local clock generation using universal serial bus downstream received signals DP and DM |

| US6748039B1 (en) | 2000-08-11 | 2004-06-08 | Advanced Micro Devices, Inc. | System and method for synchronizing a skip pattern and initializing a clock forwarding interface in a multiple-clock system |

| DE10041772C2 (de) * | 2000-08-25 | 2002-07-11 | Infineon Technologies Ag | Taktgenerator, insbesondere für USB-Geräte |

| US7093151B1 (en) | 2000-09-22 | 2006-08-15 | Cypress Semiconductor Corp. | Circuit and method for providing a precise clock for data communications |

| KR100405023B1 (ko) * | 2000-12-05 | 2003-11-07 | 옵티시스 주식회사 | 유니버셜 직렬 버스용 광통신 인터페이스 모듈 |

| US6760772B2 (en) * | 2000-12-15 | 2004-07-06 | Qualcomm, Inc. | Generating and implementing a communication protocol and interface for high data rate signal transfer |

| KR100392558B1 (ko) * | 2001-05-14 | 2003-08-21 | 주식회사 성진씨앤씨 | 복수 개의 유에스비 카메라를 이용한 피씨 기반의 디지털영상 저장 장치 시스템 |

| US6975618B1 (en) * | 2001-06-26 | 2005-12-13 | Hewlett-Packard Development Company, L.P. | Receiver and correlator used to determine position of wireless device |

| US7542867B2 (en) * | 2001-08-14 | 2009-06-02 | National Instruments Corporation | Measurement system with modular measurement modules that convey interface information |

| US7478006B2 (en) * | 2001-08-14 | 2009-01-13 | National Instruments Corporation | Controlling modular measurement cartridges that convey interface information with cartridge controllers |

| US6823283B2 (en) * | 2001-08-14 | 2004-11-23 | National Instruments Corporation | Measurement system including a programmable hardware element and measurement modules that convey interface information |

| US7165005B2 (en) * | 2001-08-14 | 2007-01-16 | National Instruments Corporation | Measurement module interface protocol database and registration system |

| US7080274B2 (en) * | 2001-08-23 | 2006-07-18 | Xerox Corporation | System architecture and method for synchronization of real-time clocks in a document processing system |

| US7251199B2 (en) | 2001-12-24 | 2007-07-31 | Agilent Technologies, Inc. | Distributed system time synchronization including a timing signal path |

| US6741952B2 (en) | 2002-02-15 | 2004-05-25 | Agilent Technologies, Inc. | Instrument timing using synchronized clocks |

| GB2385684A (en) * | 2002-02-22 | 2003-08-27 | Sony Uk Ltd | Frequency synchronisation of clocks |

| JP2003316736A (ja) * | 2002-04-19 | 2003-11-07 | Oki Electric Ind Co Ltd | Usb回路およびデータ構造 |

| US7206327B2 (en) * | 2002-05-17 | 2007-04-17 | Broadcom Corporation | Method and circuit for insertion of time stamp into real time data |

| US7395366B1 (en) * | 2002-09-27 | 2008-07-01 | Cypress Semiconductor Corp. | System, method, and apparatus for connecting USB peripherals at extended distances from a host computer |

| US7269217B2 (en) | 2002-10-04 | 2007-09-11 | Intersil Americas Inc. | PWM controller with integrated PLL |

| DE10262079A1 (de) * | 2002-12-23 | 2004-11-18 | Infineon Technologies Ag | Verfahren und Vorrichtung zum Extrahieren einer einem Datenstrom zugrundeliegenden Taktfrequenz |

| US7120813B2 (en) * | 2003-01-28 | 2006-10-10 | Robert Antoine Leydier | Method and apparatus for clock synthesis using universal serial bus downstream received signals |

| JP4377603B2 (ja) * | 2003-03-26 | 2009-12-02 | Okiセミコンダクタ株式会社 | バス通信システムおよびその通信制御方法 |

| JP3909704B2 (ja) * | 2003-04-04 | 2007-04-25 | ソニー株式会社 | 編集システム |

| US7506179B2 (en) * | 2003-04-11 | 2009-03-17 | Zilker Labs, Inc. | Method and apparatus for improved DC power delivery management and configuration |

| US7339861B2 (en) * | 2003-04-21 | 2008-03-04 | Matsushita Electric Industrial Co., Ltd. | PLL clock generator, optical disc drive and method for controlling PLL clock generator |

| JP4373267B2 (ja) * | 2003-07-09 | 2009-11-25 | 株式会社ルネサステクノロジ | スプレッドスペクトラムクロック発生器及びそれを用いた集積回路装置 |

| US7145438B2 (en) * | 2003-07-24 | 2006-12-05 | Hunt Technologies, Inc. | Endpoint event processing system |

| US20050108600A1 (en) * | 2003-11-19 | 2005-05-19 | Infineon Technologies Ag | Process and device for testing a serializer circuit arrangement and process and device for testing a deserializer circuit arrangement |

| WO2005076507A1 (en) * | 2004-02-05 | 2005-08-18 | Koninklijke Philips Electronics, N.V. | Mehtod and apparatus for synchronization over 802.3af |

| JP2005239393A (ja) * | 2004-02-27 | 2005-09-08 | Kyocera Mita Corp | 画像形成装置 |

| US7456699B2 (en) * | 2004-03-22 | 2008-11-25 | Mobius Microsystems, Inc. | Frequency controller for a monolithic clock generator and timing/frequency reference |

| US7319345B2 (en) * | 2004-05-18 | 2008-01-15 | Rambus Inc. | Wide-range multi-phase clock generator |

| US7020727B2 (en) * | 2004-05-27 | 2006-03-28 | Motorola, Inc. | Full-span switched fabric carrier module and method |

| US6978332B1 (en) * | 2004-07-02 | 2005-12-20 | Motorola, Inc. | VXS multi-service platform system with external switched fabric link |

| US20060165132A1 (en) * | 2004-11-15 | 2006-07-27 | Emin Chou | Computer peripheral interface |

| US7710965B2 (en) * | 2004-11-23 | 2010-05-04 | Broadlogic Network Technologies Inc. | Method and system for multi-program clock recovery and timestamp correction |

| US7602820B2 (en) * | 2005-02-01 | 2009-10-13 | Time Warner Cable Inc. | Apparatus and methods for multi-stage multiplexing in a network |

| US7835773B2 (en) * | 2005-03-23 | 2010-11-16 | Kyocera Corporation | Systems and methods for adjustable audio operation in a mobile communication device |

| CN100487983C (zh) * | 2005-04-13 | 2009-05-13 | 台均科技(深圳)有限公司 | 一种usb数据-音频信号复用传输线 |

| US7480126B2 (en) * | 2005-04-27 | 2009-01-20 | National Instruments Corporation | Protection and voltage monitoring circuit |

| US7366939B2 (en) * | 2005-08-03 | 2008-04-29 | Advantest Corporation | Providing precise timing control between multiple standardized test instrumentation chassis |

| US7825707B2 (en) * | 2006-01-11 | 2010-11-02 | Panasonic Corporation | Clock generation circuit having a spread spectrum clocking function |

| US7830874B2 (en) * | 2006-02-03 | 2010-11-09 | Itron, Inc. | Versatile radio packeting for automatic meter reading systems |

| US7610175B2 (en) * | 2006-02-06 | 2009-10-27 | Agilent Technologies, Inc. | Timestamping signal monitor device |

| JP2007215039A (ja) * | 2006-02-10 | 2007-08-23 | Ricoh Co Ltd | 周波数シンセサイザ、通信機、及び周波数シンセサイズ方法 |

| JP2007251228A (ja) * | 2006-03-13 | 2007-09-27 | Toshiba Corp | 電圧制御発振器、動作電流調整装置、および、電圧制御発振器の動作電流調整方法 |

| US7242590B1 (en) * | 2006-03-15 | 2007-07-10 | Agilent Technologies, Inc. | Electronic instrument system with multiple-configuration instrument modules |

| US20070217170A1 (en) * | 2006-03-15 | 2007-09-20 | Yeap Boon L | Multiple configuration stackable instrument modules |

| US20070217169A1 (en) * | 2006-03-15 | 2007-09-20 | Yeap Boon L | Clamshell housing for instrument modules |

| US7509445B2 (en) * | 2006-04-12 | 2009-03-24 | National Instruments Corporation | Adapting a plurality of measurement cartridges using cartridge controllers |

| US8660152B2 (en) | 2006-09-25 | 2014-02-25 | Futurewei Technologies, Inc. | Multi-frame network clock synchronization |

| JP5054993B2 (ja) * | 2007-02-09 | 2012-10-24 | 富士通株式会社 | 同期非同期通信網の変換装置、方法、プログラム、記録媒体及び通信システム |

| TW200841182A (en) * | 2007-04-11 | 2008-10-16 | Asustek Comp Inc | Multimedia extendable module and computer device thereof |

| EP2147382B1 (en) * | 2007-05-15 | 2012-10-31 | Chronologic Pty Ltd | Method and system for reducing triggering latency in universal serial bus data acquisition |

| AU2008251024B2 (en) * | 2007-05-15 | 2013-01-24 | Chronologic Pty Ltd | USB based synchronization and timing system |

| JP5008041B2 (ja) * | 2007-05-28 | 2012-08-22 | 学校法人日本大学 | 伝搬遅延時間測定システム |

| US7778283B2 (en) * | 2007-06-04 | 2010-08-17 | Agilent Technologies, Inc. | Timing bridge device |

| US7573342B2 (en) * | 2007-07-20 | 2009-08-11 | Infineon Technologies Ag | VCO pre-compensation |

| US8451819B2 (en) * | 2008-03-26 | 2013-05-28 | Qualcomm Incorporated | Methods and apparatus for uplink frame synchronization in a subscriber station |

| US8239581B2 (en) * | 2008-05-15 | 2012-08-07 | Seagate Technology Llc | Data storage device compatible with multiple interconnect standards |

| US8250266B2 (en) * | 2008-05-15 | 2012-08-21 | Seagate Technology Llc | Data storage device compatible with multiple interconnect standards |

| US8341303B2 (en) * | 2008-06-30 | 2012-12-25 | Intel Corporation | Asymmetrical universal serial bus communications |

| US8239158B2 (en) * | 2008-08-04 | 2012-08-07 | National Instruments Corporation | Synchronizing a loop performed by a measurement device with a measurement and control loop performed by a processor of a host computer |

| US8143936B2 (en) * | 2008-09-12 | 2012-03-27 | Intel Mobile Communications GmbH | Application of control signal and forward body-bias signal to an active device |

| TWI374350B (en) * | 2008-11-11 | 2012-10-11 | Genesys Logic Inc | Serial bus clock frequency calibration system and method |

| US9104821B2 (en) * | 2008-12-31 | 2015-08-11 | Intel Corporation | Universal serial bus host to host communications |

| TW201027351A (en) * | 2009-01-08 | 2010-07-16 | Innostor Technology Corp | Signal converter of all-in-one USB connector |

| US8407508B2 (en) * | 2009-02-18 | 2013-03-26 | Genesys Logic, Inc. | Serial bus clock frequency calibration system and method thereof |

| US20120066417A1 (en) * | 2009-05-20 | 2012-03-15 | Chronologic Pty. Ltd. | Synchronisation and trigger distribution across instrumentation networks |

| US8112571B1 (en) * | 2009-07-23 | 2012-02-07 | Cypress Semiconductor Corporation | Signal connection device and method |

| US9197023B2 (en) * | 2009-09-14 | 2015-11-24 | Cadence Design Systems, Inc. | Apparatus for enabling simultaneous content streaming and power charging of handheld devices |

| WO2011038211A1 (en) * | 2009-09-25 | 2011-03-31 | Analogix Semiconductor, Inc. | Dual-mode data transfer of uncompressed multimedia contents or data communications |

| US8719112B2 (en) * | 2009-11-24 | 2014-05-06 | Microsoft Corporation | Invocation of accessory-specific user experience |

| US7865629B1 (en) * | 2009-11-24 | 2011-01-04 | Microsoft Corporation | Configurable connector for system-level communication |

| TWI460572B (zh) * | 2009-12-04 | 2014-11-11 | Via Tech Inc | 時脈產生器以及通用串列匯流排模組 |

| US8510494B2 (en) * | 2009-12-24 | 2013-08-13 | St-Ericsson Sa | USB 3.0 support in mobile platform with USB 2.0 interface |

| US8135883B2 (en) * | 2010-01-19 | 2012-03-13 | Standard Microsystems Corporation | USB hub apparatus supporting multiple high speed devices and a single super speed device |

| US8516290B1 (en) * | 2010-02-02 | 2013-08-20 | Smsc Holdings S.A.R.L. | Clocking scheme for bridge system |

| US8428045B2 (en) * | 2010-03-16 | 2013-04-23 | Harman International Industries, Incorporated | Media clock recovery |

| JP5226722B2 (ja) * | 2010-03-26 | 2013-07-03 | 株式会社バッファロー | 記憶装置 |

| JP5153822B2 (ja) * | 2010-04-28 | 2013-02-27 | 株式会社バッファロー | 周辺機器、及び、ホスト機器と周辺機器の接続方法 |

| TWI417703B (zh) * | 2010-07-22 | 2013-12-01 | Genesys Logic Inc | 相容於通用序列匯流排協定之時脈同步方法 |

| US8560754B2 (en) * | 2010-09-17 | 2013-10-15 | Lsi Corporation | Fully integrated, low area universal serial bus device transceiver |

| CN101968779A (zh) * | 2010-09-30 | 2011-02-09 | 威盛电子股份有限公司 | 通用串行总线传输转译器及微帧同步方法 |

| US8364870B2 (en) * | 2010-09-30 | 2013-01-29 | Cypress Semiconductor Corporation | USB port connected to multiple USB compliant devices |

| US8656205B2 (en) * | 2010-10-04 | 2014-02-18 | Jmicron Technology Corp. | Generating reference clocks in USB device by selecting control signal to oscillator form plural calibration units |

| JP5917069B2 (ja) * | 2010-10-20 | 2016-05-11 | キヤノン株式会社 | 通信制御装置およびその制御方法 |

| US8452910B1 (en) * | 2010-10-21 | 2013-05-28 | Total Phase, Inc. | Capture of USB packets into separate USB protocol streams based on different USB protocol specifications |

| US9009380B2 (en) * | 2010-12-02 | 2015-04-14 | Via Technologies, Inc. | USB transaction translator with SOF timer and USB transaction translation method for periodically sending SOF packet |

| US8572306B2 (en) * | 2010-12-02 | 2013-10-29 | Via Technologies, Inc. | USB transaction translator and USB transaction translation method |

| US8825925B1 (en) * | 2011-02-14 | 2014-09-02 | Cypress Semiconductor Corporation | Systems and methods for super speed packet transfer |

| US8718088B2 (en) * | 2011-05-13 | 2014-05-06 | SiFotonics Technologies Co, Ltd. | Signal converter of consumer electronics connection protocols |

| CN102955585A (zh) * | 2011-08-24 | 2013-03-06 | 鸿富锦精密工业(深圳)有限公司 | 鼠标 |

| JP5936498B2 (ja) * | 2012-01-16 | 2016-06-22 | ルネサスエレクトロニクス株式会社 | Usb3.0デバイス及び制御方法 |

| US20130191568A1 (en) * | 2012-01-23 | 2013-07-25 | Qualcomm Incorporated | Operating m-phy based communications over universal serial bus (usb) interface, and related cables, connectors, systems and methods |

| TWI443494B (zh) * | 2012-04-16 | 2014-07-01 | M31 Technology Corp | Clock Generation Method and System Using Pulse Wave Identification |

| CN103294636A (zh) * | 2012-05-09 | 2013-09-11 | 威盛电子股份有限公司 | 集线器控制芯片 |

| US8930585B2 (en) * | 2012-05-29 | 2015-01-06 | Mediatek Inc. | USB host controller and scheduling methods thereof |

| US8959272B2 (en) * | 2012-07-06 | 2015-02-17 | Blackberry Limited | Interposer and intelligent multiplexer to provide a plurality of peripherial buses |

| KR20140065074A (ko) * | 2012-11-21 | 2014-05-29 | 삼성전자주식회사 | 모바일 디바이스 및 유에스비 허브 |

| TWI598738B (zh) * | 2012-12-24 | 2017-09-11 | 宏碁股份有限公司 | 介面擴充裝置 |

| CN203102268U (zh) * | 2013-01-30 | 2013-07-31 | 青岛汉泰电子有限公司 | 带触发和时钟同步功能的控制总线 |

| US8954623B2 (en) * | 2013-04-23 | 2015-02-10 | Mediatek Inc. | Universal Serial Bus devices supporting super speed and non-super speed connections for communication with a host device and methods using the same |

| KR20150009239A (ko) * | 2013-07-16 | 2015-01-26 | 삼성전자주식회사 | 화상형성장치의 내부 인터페이스 |

-

2010

- 2010-05-20 US US13/320,388 patent/US20120066417A1/en not_active Abandoned

- 2010-05-20 AU AU2010251767A patent/AU2010251767A1/en not_active Abandoned

- 2010-05-20 WO PCT/AU2010/000603 patent/WO2010132942A1/en active Application Filing

- 2010-05-20 EP EP10777233.7A patent/EP2433196B1/en not_active Not-in-force

- 2010-05-20 EP EP10777234.5A patent/EP2433197B1/en not_active Not-in-force

- 2010-05-20 WO PCT/AU2010/000607 patent/WO2010132946A1/en active Application Filing

- 2010-05-20 US US13/320,401 patent/US8667316B2/en not_active Expired - Fee Related

- 2010-05-20 US US13/321,707 patent/US8984321B2/en not_active Expired - Fee Related

- 2010-05-20 AU AU2010251774A patent/AU2010251774A1/en not_active Abandoned

- 2010-05-20 CN CN2010800219269A patent/CN102439531A/zh active Pending

- 2010-05-20 CN CN2010800218675A patent/CN102428423A/zh active Pending

- 2010-05-20 WO PCT/AU2010/000602 patent/WO2010132941A1/en active Application Filing

- 2010-05-20 WO PCT/AU2010/000600 patent/WO2010132939A1/en active Application Filing

- 2010-05-20 EP EP14165614.0A patent/EP2800004A1/en not_active Withdrawn

- 2010-05-20 EP EP14170487.4A patent/EP2800005A1/en not_active Withdrawn

- 2010-05-20 EP EP10777231.1A patent/EP2432754B1/en not_active Not-in-force

- 2010-05-20 AU AU2010251776A patent/AU2010251776A1/en not_active Abandoned

- 2010-05-20 JP JP2012511096A patent/JP5575229B2/ja not_active Expired - Fee Related

- 2010-05-20 CA CA2761363A patent/CA2761363A1/en not_active Abandoned

- 2010-05-20 WO PCT/AU2010/000599 patent/WO2010132938A1/en active Application Filing

- 2010-05-20 AU AU2010251772A patent/AU2010251772A1/en not_active Abandoned

- 2010-05-20 CA CA2761379A patent/CA2761379A1/en not_active Abandoned

- 2010-05-20 JP JP2012511097A patent/JP2012527660A/ja active Pending

- 2010-05-20 US US13/320,334 patent/US8626980B2/en not_active Expired - Fee Related

- 2010-05-20 US US13/320,346 patent/US8793524B2/en not_active Expired - Fee Related

- 2010-05-20 WO PCT/AU2010/000605 patent/WO2010132944A1/en active Application Filing

- 2010-05-20 WO PCT/AU2010/000608 patent/WO2010132947A1/en active Application Filing

- 2010-05-20 JP JP2012511095A patent/JP5636043B2/ja not_active Expired - Fee Related

- 2010-05-20 EP EP10777236.0A patent/EP2433198B1/en not_active Not-in-force

- 2010-05-20 US US13/320,437 patent/US20120066418A1/en not_active Abandoned

- 2010-05-20 CA CA2761377A patent/CA2761377A1/en not_active Abandoned

- 2010-05-20 WO PCT/AU2010/000606 patent/WO2010132945A1/en active Application Filing

- 2010-05-20 WO PCT/AU2010/000604 patent/WO2010132943A1/en active Application Filing

- 2010-05-20 AU AU2010251769A patent/AU2010251769B2/en not_active Ceased

- 2010-05-20 AU AU2010251773A patent/AU2010251773A1/en not_active Abandoned

- 2010-05-20 US US13/320,279 patent/US8745431B2/en not_active Expired - Fee Related

- 2010-05-20 WO PCT/AU2010/000601 patent/WO2010132940A1/en active Application Filing

- 2010-05-20 EP EP10777229.5A patent/EP2433193B1/en not_active Not-in-force

- 2010-05-20 CN CN2010800219729A patent/CN102439532A/zh active Pending

- 2010-05-20 EP EP10777227.9A patent/EP2433194B1/en not_active Not-in-force

- 2010-05-20 EP EP10777232.9A patent/EP2433195B1/en not_active Not-in-force

- 2010-05-20 EP EP14175684.1A patent/EP2790110A1/en not_active Withdrawn

- 2010-05-20 AU AU2010251771A patent/AU2010251771A1/en not_active Abandoned

-

2014

- 2014-04-17 US US14/255,646 patent/US20140229756A1/en not_active Abandoned

- 2014-06-12 US US14/303,069 patent/US20140298072A1/en not_active Abandoned

- 2014-06-25 JP JP2014130363A patent/JP2014197421A/ja active Pending

- 2014-09-15 US US14/486,513 patent/US20150039791A1/en not_active Abandoned

- 2014-12-01 US US14/557,150 patent/US20150089098A1/en not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6092210A (en) * | 1998-10-14 | 2000-07-18 | Cypress Semiconductor Corp. | Device and method for synchronizing the clocks of interconnected universal serial buses |

| CN101281512A (zh) * | 2002-07-17 | 2008-10-08 | 菲博比特有限公司 | 同步多信道通用串行总线 |

| CN101401055A (zh) * | 2006-02-15 | 2009-04-01 | 菲博比特有限公司 | 分布式同步和定时系统 |

Non-Patent Citations (1)

| Title |

|---|

| HEWLEFT-PACKARD COMPANY ET AL.: "《Universal Serial Bus 3.0 Specification,Revision 1.0》", 12 November 2008, article "Universal Serial Bus 3.0 Specification,Revision 1.0", pages: (3-1)-(3-12) * |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103309397A (zh) * | 2013-06-17 | 2013-09-18 | 杭州锐达数字技术有限公司 | 基于usb的数据采集设备的同步采样方法 |

| CN103309397B (zh) * | 2013-06-17 | 2015-11-18 | 杭州锐达数字技术有限公司 | 基于usb的数据采集设备的同步采样方法 |

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102439532A (zh) | 超高速和非超高速usb装置的同步网络 | |

| JP5231255B2 (ja) | 分散型の同期およびタイミングシステム | |

| CN1679013B (zh) | 同步多信道通用串行总线 | |

| CN101103278B (zh) | 具有同步仪器的自动测试系统 | |

| KR20000075817A (ko) | 버스 브리지에서 복수의 버스 노드들에 사이클 클럭을 분포시키는 방법 및 장치 | |

| CN103929263A (zh) | 网络通信方法、延迟确定方法、本地时间同步方法 | |

| CN101103277A (zh) | 自动测试设备中具有用于同步的接口的仪器 | |

| CN102271019A (zh) | 通过光纤进行的精密时间传递 | |

| CN101009546A (zh) | 采用不同时间同步协议的网段间实现时间同步的方法 | |

| CN107968693B (zh) | 一种时间频率同步设备扩展输出系统 | |

| JP4726956B2 (ja) | I/o装置によるネットワークシステムの通信方法 | |

| CN104980243A (zh) | 一种实现多时间源输出灵活授时系统的方法及装置 | |

| CN209844975U (zh) | 一种核心工业以太网交换机时钟对时装置 | |

| CN108668183B (zh) | 一种光网络同步测试方法和系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: DE Ref document number: 1169501 Country of ref document: HK |

|

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Application publication date: 20120502 |

|

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: WD Ref document number: 1169501 Country of ref document: HK |